# MRI (# 1625499): Design of Configuration and Readout Electronics for a Multi-Channel Integrated Circuit used in the Detection and Monitoring of Ionization Radiation

**Advisor : Dr. George L Engel**

By

Sai Geetha Allipuram

Department of Electrical and Computer Engineering

### **Outline**

- Introduction

- System Level Design

- Digital Design using EDI Tools

- Standard Cell Design Flow

- Common Channel

- Signal Channel

- Summary

- Future Work

### **Introduction**

#### Research Background:

- Alliance of IC Design Research Laboratory at SIUE with the Nuclear Reactions Group at Washington University St. Louis

- Development of a class of multi-channel custom integrated circuits

(ICs)

- Need for these custom IC's ?

- The Collaboration Achievements:

- **HINP** Heavy Ion Nuclear Physics with 16 Channels

- **PSD** Pulse Shape Discrimination with 8 Channels

- Later many revised versions of PSD8C and HINP16C are developed

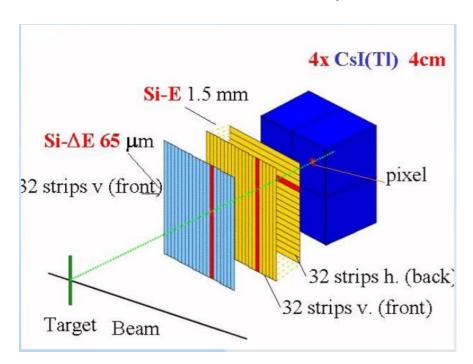

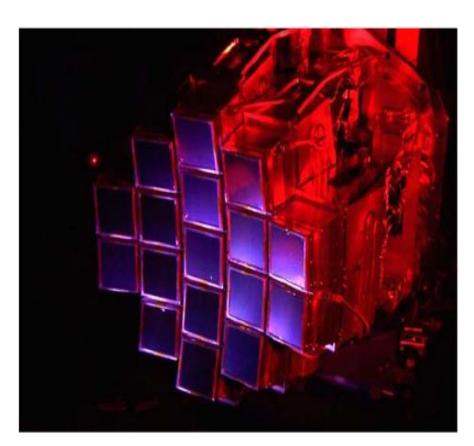

- HiRA High Resolution Array Detector

- An Array of Silicon Strip Detectors

- 2 Silicon detectors of 65 μm & 1.5 mm

Fig.2 A look at Silicon Strip Detectors in HiRA © Stephanie\_Simpson

Fig.1 HiRA – High Resolution Array Detector

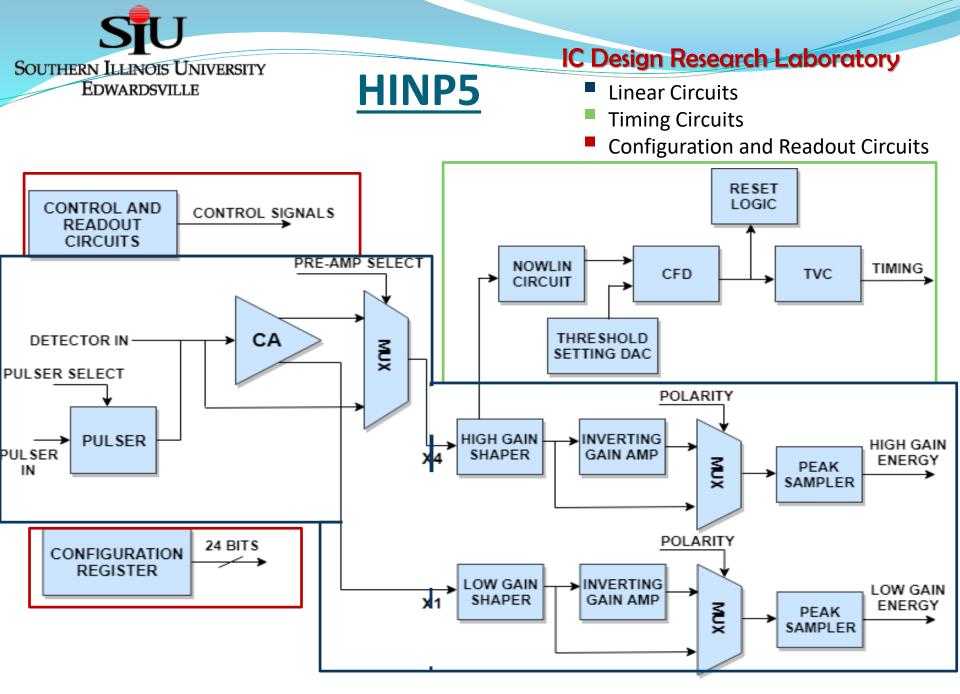

Fig.3 Block Diagram of a typical HINP5 channel © Korkmaz Anil

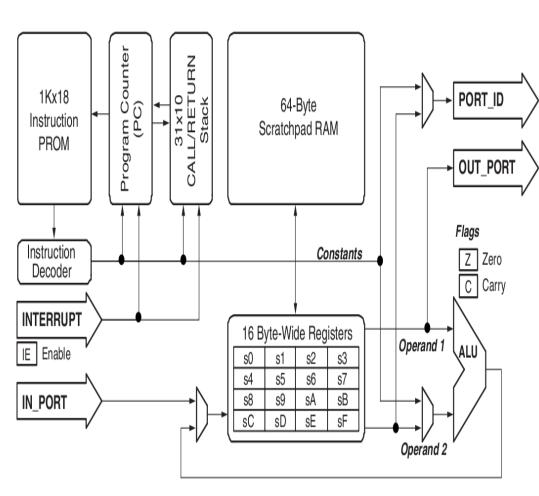

#### **High Level System Design**

- HINP5 chip generates analog pulse trains for both timing and energy of incident radiation.

- Need for digitization ?

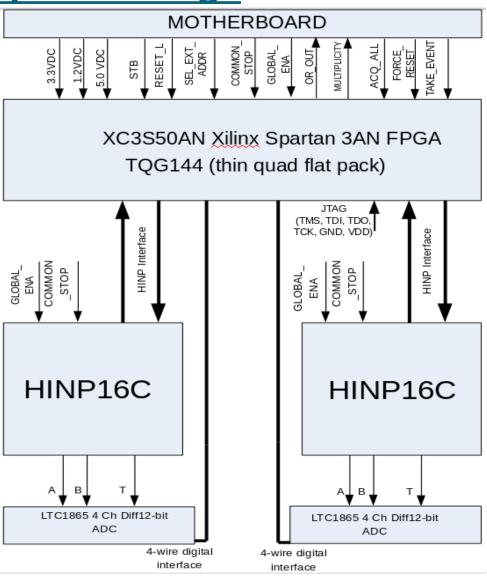

- The Chipboards has

- A simple Xilinx FPGA

- 2 HINP5 chips

- 3 ADC's for each HINP5 chip

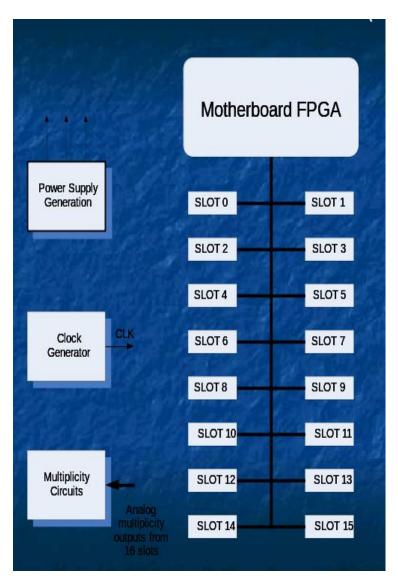

Fig.4 Block Diagram of the System

#### **Digital Design using EDI Tools**

- A Verilog driven digital design

- Cadence's EDI(Encounter Digital Implementation) computer aided design tools.

- Standard cell design approach

- Why Standard Cell Design ?

- Building blocks: Logic cells from the digital standard cell library.

- Less amount of design effort.

- Speeds-up the design phase of the digital circuits[Eriksson et al., 2019].

### **Standard Cell Design Approach**

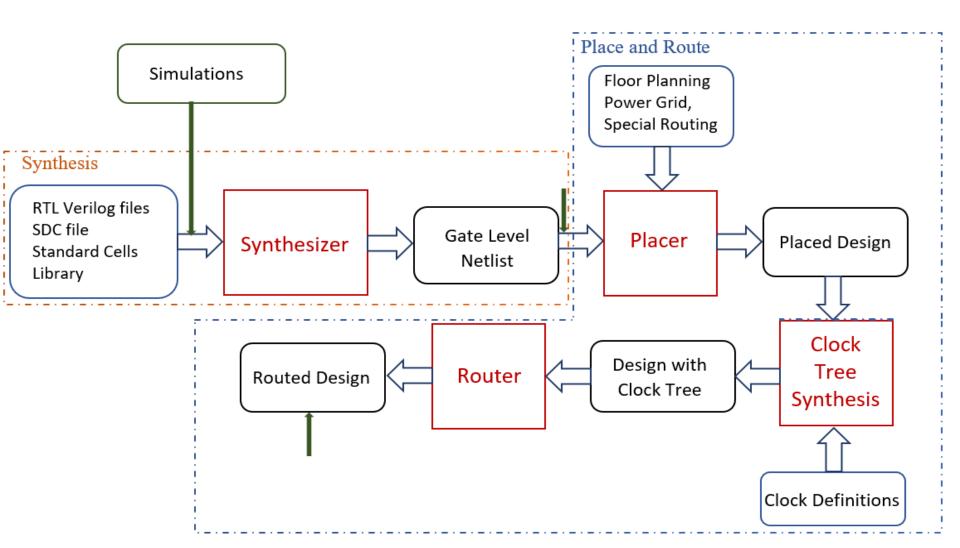

Fig.7 Standard Cell Design Flow

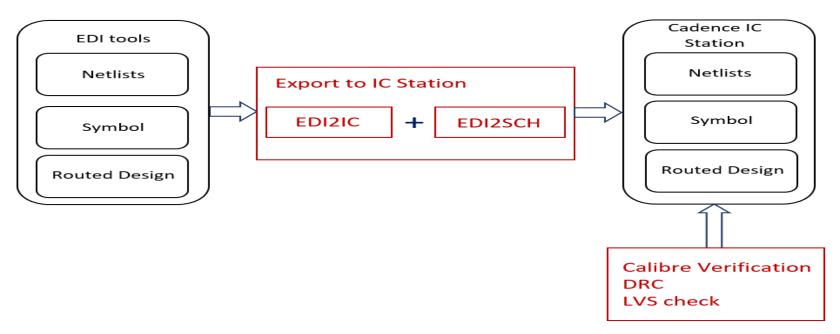

Fig.8 Exporting the design from cadence EDI tools to Cadence IC station

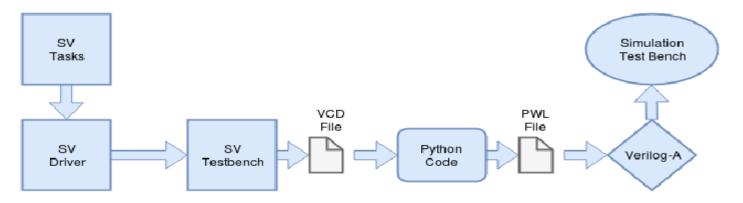

Fig.9 Electrical Simulation testing procedure © Bryan Orabutt

stb L

#### **Common channel**

HINP Digital

input ad\_in [7:0]

input write

input stb

input hit [15:0]

input reset\_L

input force\_reset

input common\_bus[7:0]

output ad\_out [7:0]

output chan\_sel [15:0]

output stb\_L

output load\_dac

output read\_dac

output or\_out

output drive\_output\_buffer

output config\_reg\_0 [7:0]

output config\_reg\_1 [7:0]

output config\_reg\_2 [7:0]

output dec\_out [15:0]

#### **Configuration and Readout Electronics**

- Provides proper control signals

- for all the sixteen signal channels and does readout.

- 24 Configuration bits

- Readout electronics

| Configuration<br>Register | BIT<br>Position | Name             | Function                                                                                       |

|---------------------------|-----------------|------------------|------------------------------------------------------------------------------------------------|

| config_reg_0              | 0               | USE_EVEN_PULSER  | 0: Default<br>1: Pulsing EVEN channels                                                         |

| config_reg_0              | 1               | USE_ODD_PULSER   | 0: Default<br>1: Pulsing ODD channels                                                          |

| config_reg_0              | 2               | NOWLIN_CAP0      | Selects one of the 16                                                                          |

| config_reg_0              | 3               | NOWLIN_CAP1      | capacitors to                                                                                  |

| config_reg_0              | 4               | NOWLIN_CAP2      | Set the NOWLIN delay (                                                                         |

| config_reg_0              | 5               | NOWLIN_CAP3      | 0.5pF to 8 pF)                                                                                 |

| config reg 0              | 6               | NOWLIN MODE      | 0: Long Mode (Rise time constant: 12ns – 192ns) 1: Short Mode (Rise time constant: 1ns - 16ns) |

| coming_reg_0              | U               | INO WEIIN_IVIODE | •                                                                                              |

| config_reg_0              | 7               | BUFFER_BIAS_HG   | 0: Bias is 50mv<br>1: Bias is 25mv                                                             |

Table.1 Bit assignments of configuration register **cr\_reg\_0**

|                           | KDSVILLE        |                         |                                                                             | Configuratio  |                 |                     |                                                                                    |

|---------------------------|-----------------|-------------------------|-----------------------------------------------------------------------------|---------------|-----------------|---------------------|------------------------------------------------------------------------------------|

| Configuration<br>Register | BIT<br>Position | Name                    | Function                                                                    | n<br>Register | BIT<br>Position | Name                | Function                                                                           |

| Register                  | Position        | Name                    | runction                                                                    | Register      | POSITION        | Name                | runction                                                                           |

| config_reg_1              | 0               | BUFFER_BIAS_HG_PO       | <ul><li>0: Positive Polarity</li><li>1: Negative</li><li>Polarity</li></ul> | config_reg_2  | 0               | TVC_2_USEC_<br>MODE | 1: TVC 2 usec full range<br>0: TVC 250 nsec range                                  |

| config_reg_1              | 1               | BUFFER_BIAS_LG          | 0: Bias is 50mv<br>1: Bias is 25mv                                          | config_reg_2  | 1               | EXT_CHARGE_<br>AMP  | 0: Use internal charge amp<br>1: Use external charge amp                           |

| config_reg_1              | 2               | BUFFER_BIAS_LG_PO<br>L  | 0: Positive Polarity<br>1: Negative<br>Polarity                             | config_reg_2  | 2               | HOLES               | 0: Electrons Collection 1: Holes Collection                                        |

| config_reg_1              | 3               | BUFFER_BIAS_TVC         | 0: Bias is 50mv<br>1: Bias is 25mv                                          | config_reg_2  | 3               | DLY_VC0             | 4-bit value that determines                                                        |

| config_reg_1              | 4               | BUFFER_BIAS_TVC_P<br>OL | 0: Positive Polarity<br>1: Negative<br>Polarity                             | config_reg_2  | 4               | DLY_VC1             | the 16 delay times by the auto reset block before the channels auto                |

| config_reg_1              | 5               | AGND_TR0                |                                                                             | config_reg_2  | 5               | DLY_VC2             | reset.                                                                             |

| config_reg_1              | 6               | AGND_TR1                | Allows to adjust<br>AGND voltage ( 1.4                                      | config_reg_2  | 6               | DLY_VC3             |                                                                                    |

|                           |                 |                         | to 1.8v in 50mV<br>step)                                                    |               |                 |                     | 1 bit that determines the width of the digital reset to be either 100nsec or 1usec |

| config_reg_1              | 7               | AGND_TR2                |                                                                             | config_reg_2  | /               | DLY_VC4             |                                                                                    |

Table.2 Bit assignments of configuration registers cr\_reg\_1 & cr\_reg\_2

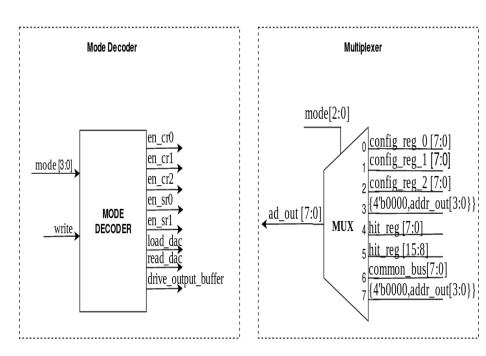

#### **Modes of Operation**

| write  | mode[2:0]      | Operation                                    |

|--------|----------------|----------------------------------------------|

| 0      | "000"          | ad_out < config_reg_0[7:0]                   |

| 0      | "001"          | ad_out < config_reg_1[7:0]                   |

| 0      | "010"          | ad_out < config_reg_2[7:0]                   |

| 0      | "011"          | ad_out < {addr_out[3:0], 4'b000}             |

| 0      | "100"          | ad_out < hit_reg_lower[7:0]                  |

| 0      | "101"<br>"110" | ad_out < hit_reg_upper[7:0]<br>ad_out < 8'd0 |

| 0      | "111"          | ad_out < {addr_out[3:0] , 4'b0000}           |

| 1      | "000"          | config_reg_0 < ad_in[7:0]                    |

| 1      | "001"          | config_reg_1 < ad_in[7:0]                    |

| 1      | "010"          | config_reg_2 < ad_in[7:0]                    |

| 1      | "011"          | addr_in < ad_in[7:4]                         |

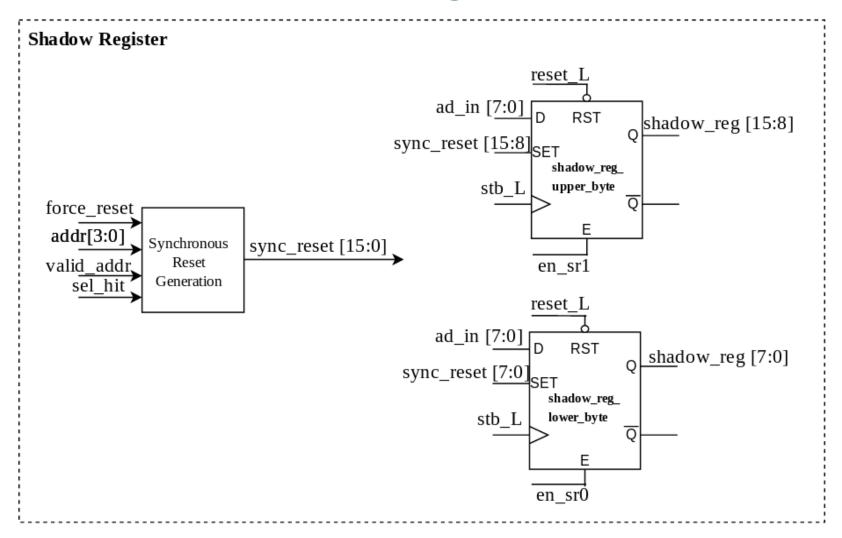

| 1      | "100"          | shadow_reg_lower < ad_in[7:0]                |

| 1      | "101"          | shadow_reg_upper < ad_in[7:0]                |

| 1<br>1 | "110"<br>"111" | dac_reg(addr) < ad_in[7:0]                   |

| 1      | TTT            | addr_in < ad_in[7:4]                         |

Table 3. Modes of Operation

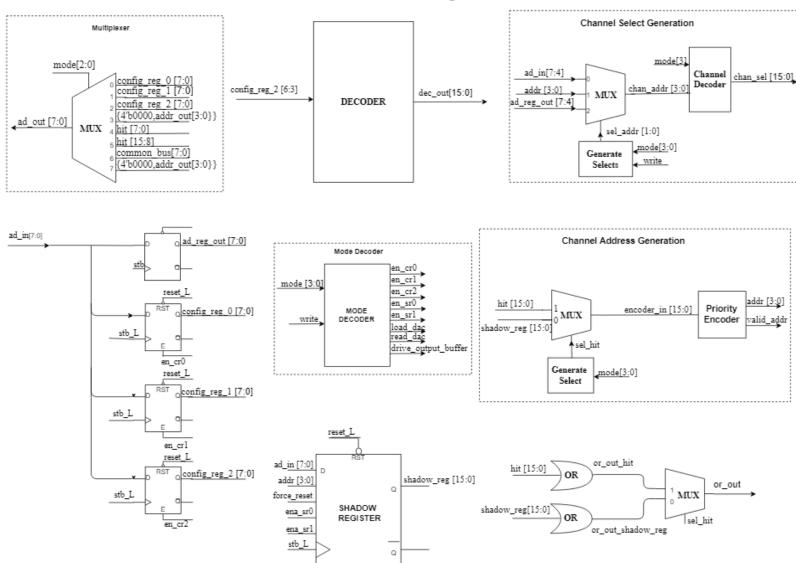

Fig.11 Mode Decoding Circuit in common channel

#### ad\_reg [7:0] <--- {addr, mode}

addr: Upper nibble of ad\_reg

mode: Lower nibble of ad\_reg

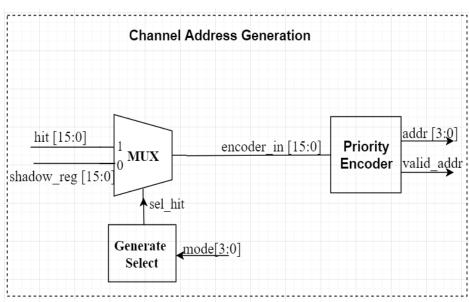

### **Channel Address Generation**

#### Verilog logic of channel address generation

```

/**** Digital Logic for Channel Address Generation ****/

// MUX Logic for choosing either hit register or shadow register

reg [15:0] encoder in;

always @(*) begin

case (sel hit)

0: encoder in = shadow reg;

1: encoder in = hit;

endcase

.// Generate sel hit bit for choosing either hit register or shadow register

assign sel hit = (mode[2:0] == 3'd3 & ~write)? 1'b0 : 1'b1;

// Priority Encoder Block

integer j;

always @(*) begin

if (|encoder in) begin

for (j=15; j>=0 ; j=j-1) begin

if (encoder in[j]) begin

addr = i:

valid addr = 1'b1;

end

end

end

else begin

addr = 4'd0:

valid addr = 1'b0;

end

```

Fig.12 Channel Address Generation Circuit

#### **Example:**

If odd channels are hit;

| $hit[15:0] \rightarrow encoder_in[15:0]$ | addr[3:0] | valid_addr |  |  |

|------------------------------------------|-----------|------------|--|--|

| 1010_1010_1010_1010                      | 0001      | 1          |  |  |

| readout;                                 |           |            |  |  |

| $hit[15:0] \rightarrow encoder_in[15:0]$ | addr[3:0] | valid_addr |

|------------------------------------------|-----------|------------|

| 1010_1010_1010_1000                      | 0011      | 1          |

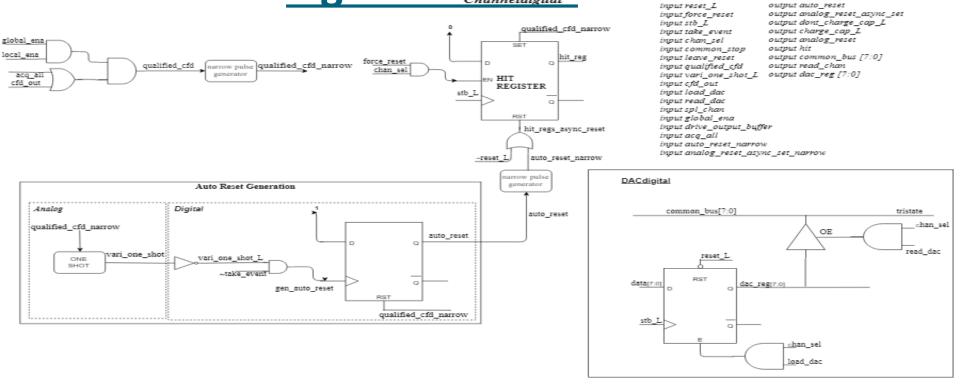

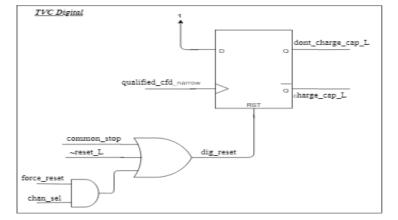

### Signal Channel

### Layout of HINPdigital

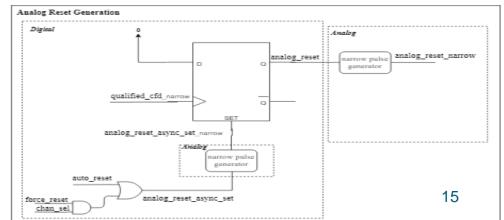

Fig.15 Layout of HINP common channel digital logic generated by place & route tool

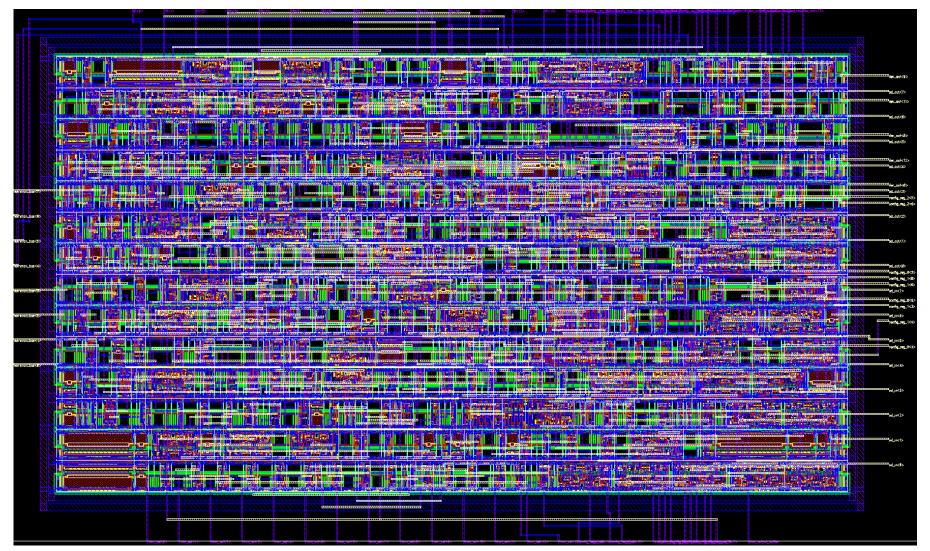

### Layout of Channeldigital

Fig.16 Layout of HINP signal channel digital logic generated by place & route tool

### **Summary**

- Layout Dimensions:

- HINP Digital: 427 μm X 223 μm

- Channel Digital: 191 μm X 119 μm

- A Verilog driven design carried out using cadence EDI tools and digital standard cell library in 0.35-micron AMS design Kit.

- Electronic simulation performed using NC-Sim to verify the behavioral description of the digital logic implemented.

- Electrical simulations were also performed on the digital designs.

- The simulation results are as expected with out any issues.

### **Future Work**

- Enhance the current SDC (Synopsys Design Constraints) file.

- The configuration and readout electronics digital design need to be binded with other analog circuits in the chip.

- Chip level simulations including the parasitic extraction still need to be done.

- Final Layouts of the HINP5 chip need to be finished.

- Expected to send for fabrication in late 2019 submissions to MOSIS.

## Queries?

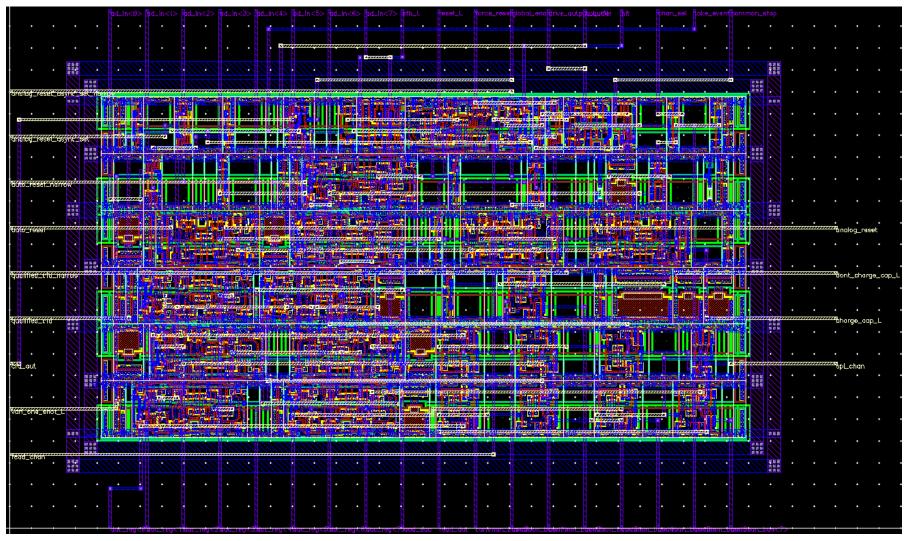

Fig.5 Block Diagram of the Motherboard

Fig.6 An 8-bit Pico blaze embedded microcontroller in FPGA.

### **Shadow Register**

Fig. 10 Shadow register in common channel

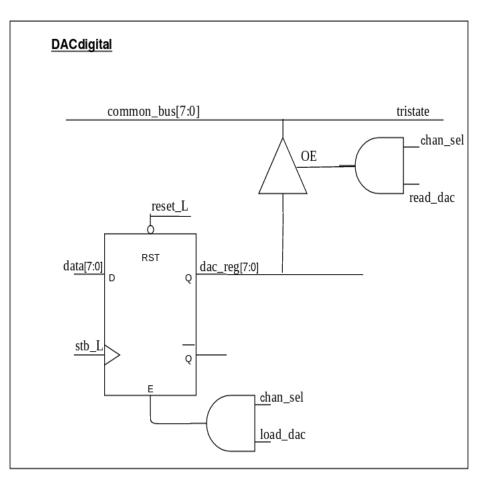

### **DAC Digital**

| Bit<br>Position  | Name                            | Function                                                                                               |

|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3 | DATA[0] DATA[1] DATA[2] DATA[3] | 5-bit value that sets the threshold for the DAC at what level cfd fires                                |

| 5                | DATA[4]  DATA[5]                | This bit sets the polarity of the DAC 0: Positive Polarity 1: Negative Polarity                        |

| 6                | LOCAL_EN<br>A                   | <ul><li>0: Disables the signal channel locally</li><li>1: Enables the signal channel locally</li></ul> |

| 7                | UNUSED                          | UNUSED                                                                                                 |

Fig.13 DAC digital circuit in signal channel