# Design of the Configuration and Readout Electronics for a Multi-Channel Integrated Circuit Used in the Detection and Monitoring of Ionizing Radiation

by SaiGeetha Allipuram, Bachelor of Science

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in the field of Electrical Engineering

Advisory Committee:

George L. Engel, Ph.D, Chair

Bradley Noble, D.Sc

Timothy York, Ph.D

$\begin{array}{c} {\rm Graduate~School} \\ {\rm Southern~Illinois~University~Edwards ville} \\ {\rm May,~2019} \end{array}$

© Copyright by SaiGeetha Allipuram May, 2019 All rights reserved

#### ABSTRACT

DESIGN OF THE CONFIGURATION AND READOUT ELECTRONICS FOR A MULTI-CHANNEL INTEGRATED CIRCUIT USED IN THE DETECTION AND MONITORING OF IONIZING RADIATION

by

## SAIGEETHA ALLIPURAM

Chairperson: Professor George L. Engel, Ph.D

This thesis describes the design of the configuration and readout electronics for a multi-channel integrated circuit (IC) which is used in the detection and monitoring of ionizing radiation in low- and intermediate-energy nuclear physics experiments. The sixteen channel chip discussed in this thesis can be used in a wide variety of nuclear physics applications and is suitable for use whenever silicon strip detectors are employed.

The chip can be used to determine the energy of a charged particle striking the detector, as well as, the time interval between the arrival of the particle at the detector and an externally supplied time reference. The configuration and readout circuits, common to all of the sixteen signal processing channels, as well as the digital logic contained within a single signal processing channel, was implemented using the Verilog Hardware Description Language (HDL) and a 0.35  $\mu m$  standard cell library. Moreover, the IC christened HINP5 (Heavy Ion Nuclear Physics chip - Version 5), will be fabricated using the AMS (Austrian Microsystems) 0.35  $\mu m$  CMOS process in the Fall of 2019.

ii

The IC is configured via three 8-bit configuration registers. Moreover, each channel contains a 6-bit Digital-to-Analog Converter (DAC) which must be programmed to set a threshold used by the Constant Fraction Discriminator (CFD), located in the timing branch within each channel. The IC supports data sparsification where a channel automatically resets itself (after a programmable delay time) unless explicitly directed to enter readout mode by an externally generated control signal.

The Verilog-driven design described in this thesis was implemented using Cadence's EDI (Encounter Digital Implementation) tools for synthesis and place n' route. The standard cell designs were then imported into Cadence's Virtuoso custom IC tools and validated at the electrical level. The use of the a standard cell approach greatly reduced design time and allows for changes to be made easily to the readout and configuration logic.

#### ACKNOWLEDGEMENTS

I would like to convey my sincere gratitude to Professor Dr. George Engel for mentoring me in every phase of my Master's study. His guidance helped me when I was struggling during my research and also during the writing of this thesis. I could not have envisioned a better mentor for my Master's work. I also wish to thank Dr. Lee Sobotka, Mr. Jon Elson, and Dr. Robert Charity (Department of Chemistry at Washington University Saint Louis) for their constant support in this project. I would like to thank my fellow graduate students: Bryan Orabutt, Lakshmi Teja Vipparla, Jayasurya Burla, Anil Korkmaz, Monjour Rafi, Lohith Chowdary Chilukuri and all of the others who contributed to the design of the HINP5 chip.

I wish to thank the National Science Foundation (NSF) for supporting my research through NSF-MRI Grant # 1625499. I would also like to thank Dr. Timothy York, Dr. Bradley Noble, Dr. Robert Leander, and the ECE faculty members at SIUE, who have supported me throughout my education at SIUE. With their support, I was able to explore new horizons.

I would not have achieved my goals without my companions Dheeraj, Vaibav, Lavanya, Sindhu, and Sohan who have supported me during my graduate studies. Finally, I would like to extend my appreciation to my family: my father Venkat Reddy Allipuram, mother, sister and brother are always with me in every aspect.

# TABLE OF CONTENTS

| ABSTR  | RACT                                      | ii       |

|--------|-------------------------------------------|----------|

| ACKNO  | OWLEDGEMENTS                              | iv       |

| LIST O | OF FIGURES                                | viii     |

| LIST O | OF TABLES                                 | ix       |

| Chapte | r                                         |          |

| 1.     | INTRODUCTION                              | 1        |

|        | 1.1 Research Background                   | 1        |

|        | 1.2 HINP IC                               | 3        |

|        | 1.2.1 Linear circuits                     | 4        |

|        | 1.2.2 Timing circuits                     | 6        |

|        | 1.2.3 Configuration and readout circuits  | 6        |

|        | 1.3 Previous Work                         | 7        |

|        | 1.4 Object and Scope of Work              | 8        |

| 2.     | SYSTEM LEVEL DESIGN                       | 10       |

|        | 2.1 Introduction                          | 10       |

|        | 2.2 System Operation                      | 10       |

|        | 2.3 MotherBoard                           | 13       |

|        | 2.4 Chipboard FPGA                        | 15       |

|        | 2.5 PicoBlaze Soft Core                   | 16       |

|        | 2.6 HINP Interface                        | 20       |

|        | 2.7 Analog-to-Digital Converter           | 21       |

| 3.     | COMMON CHANNEL                            | 24       |

|        | 3.1 Digital Design Using EDI Tools        | 25<br>25 |

|        | 3.1.2 Standard Cell Design Flow           | 26       |

|        | 3.2 Configuration and Readout Electronics | 31       |

|        | 3.2.1 Address Register                    | 31       |

|        | 3.2.2 Configuration Registers             | 33       |

|        | 3.2.3 Mode Decoding Circuitry             | 37       |

|        | 3.2.4 Shadow Register                     | 41       |

|        | 3.2.5 OR Generation                       | 42       |

|        | 3.2.6 Channel Address Generation Circuitry                                                                   | 43<br>45 |

|--------|--------------------------------------------------------------------------------------------------------------|----------|

|        | 3.2.8 4-to-16 Decoder                                                                                        | 46       |

| 4.     | SIGNAL CHANNEL                                                                                               | 47       |

|        | 4.1 Hit Register                                                                                             | 47       |

|        | 4.2 Auto Reset Generation                                                                                    | 49       |

|        | 4.3 Analog Reset Generation                                                                                  | 49       |

|        | 4.4 DAC                                                                                                      | 50       |

| 5.     | SUMMARY. CONCLUSIONS, AND FUTURE WORK                                                                        | 55       |

|        | 5.1 Summary                                                                                                  | 55       |

|        | 5.2 Conclusions                                                                                              | 55       |

|        | 5.3 Future Work                                                                                              | 57       |

| REFEF  | RENCES                                                                                                       | 6.       |

| A DDEN | IDICEC                                                                                                       | e s      |

| APPEr  | NDICES                                                                                                       | 63       |

| Α.     | Verilog Description of Digital Design Implemented in HINP5                                                   | 63       |

|        | A.1 Verilog description of the digital circuits in common channel                                            | 63       |

|        | A.1.1 Verilog description of shadow register                                                                 | 66       |

|        | A.2 Verilog description of the digital circuits in a signal channel A.3 Verilog description of HINP channels | 67<br>68 |

|        | A.5 vernog description of fiffvi channels                                                                    | UC       |

| В.     | System Verilog Test Fixture for Verification                                                                 | 7        |

|        | B.1 SystemVerilog definition of global parameters                                                            | 7        |

|        | B.2 SystemVerilog tasks                                                                                      | 72       |

|        | B.3 SystemVerilog test bench for verification                                                                | 78       |

| С.     | SDC Constraints                                                                                              | 83       |

|        | C.1 HINPdigital SDC file                                                                                     | 83       |

|        | C.2 Channeldigital SDC file                                                                                  | 83       |

| D.     | Environment Files Used in Design                                                                             | 85       |

|        | D.1 Env file for a HINP digital design used in HINP Chip in TCL                                              | 85       |

|        | D.2 Env file for a Channel digital design used in HINP Chip in TCL                                           | 8        |

| Ε. | TCL Scripts for EDI                                                  | 90       |

|----|----------------------------------------------------------------------|----------|

|    | E.1 TCL Script to run Simulation                                     | 91<br>91 |

| F. | Scripts to Generate Piece Wise Linear files from the VCD Dump file . | 94       |

|    | F.1 Make VCD TCL Script                                              | 94<br>97 |

# LIST OF FIGURES

| Figure |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

| 1.1    | An array of si strip detectors                                          | 2    |

| 1.2    | Block diagram of typical HINP5 channel[Korkmaz, 2019]                   | 5    |

| 2.1    | Block Diagram of the System                                             | 12   |

| 2.2    | Block Diagram of the MotherBoard                                        | 13   |

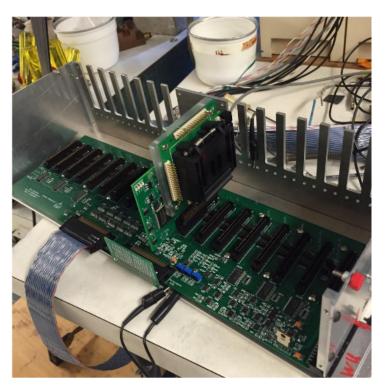

| 2.3    | Chipboard connected to one of the 16 slots on motherboard               | 14   |

| 2.4    | Spartan 3AN Architecture                                                | 16   |

| 2.5    | PicoBlaze Embedded Microcontroller                                      | 18   |

| 2.6    | PicoBlaze top-level Interface Connections                               | 19   |

| 2.7    | Channel Selection Bits in LTC1865                                       | 22   |

| 2.8    | Operating Sequence Diagram                                              | 23   |

| 3.1    | An example of a VCD file                                                | 30   |

| 3.2    | Generic schematic of logic that resides in the common channel           | 32   |

| 3.3    | Mode Decoding Logic implementation in common channel                    | 37   |

| 3.4    | Shadow Register                                                         | 42   |

| 3.5    | Circuit that generates OR_OUT signal                                    | 43   |

| 3.6    | Channel Address Generation Circuit                                      | 43   |

| 3.7    | Channel Select Generation Circuit                                       | 45   |

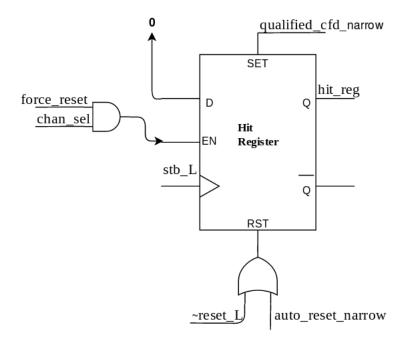

| 4.1    | Hit Register                                                            | 48   |

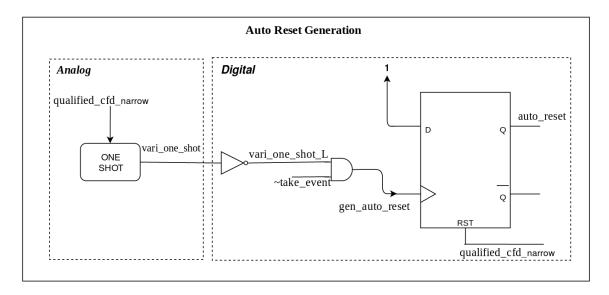

| 4.2    | Auto Reset Generation Circuitry                                         | 49   |

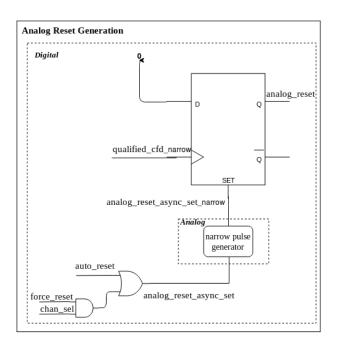

| 4.3    | Analog Reset Generation Circuitry                                       | 50   |

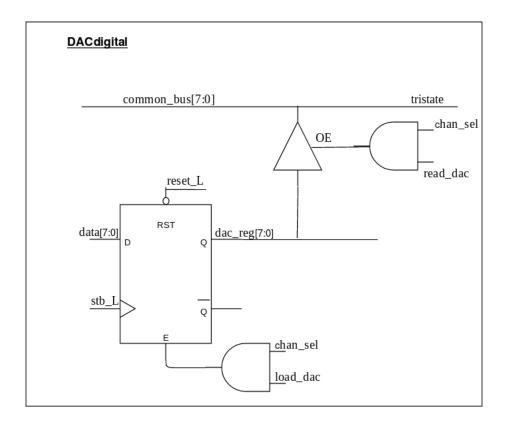

| 4.4    | DAC Register                                                            | 52   |

| 4.5    | Generic schematic of the digital logic in the HINP5 signal channel $$ . | 54   |

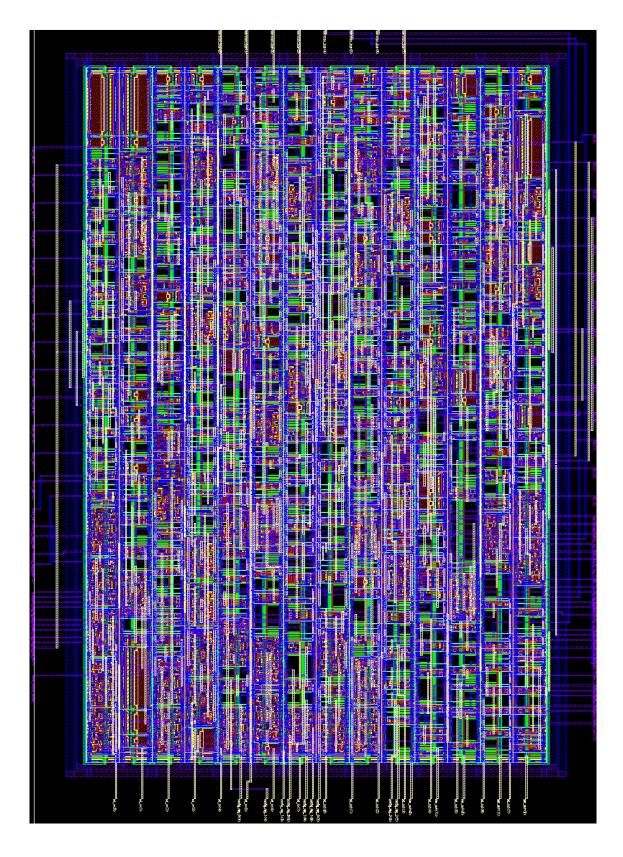

| 5.1    | Layout of the HINP common channel digital logic generated by            |      |

|        | the place n route tool                                                  | 58   |

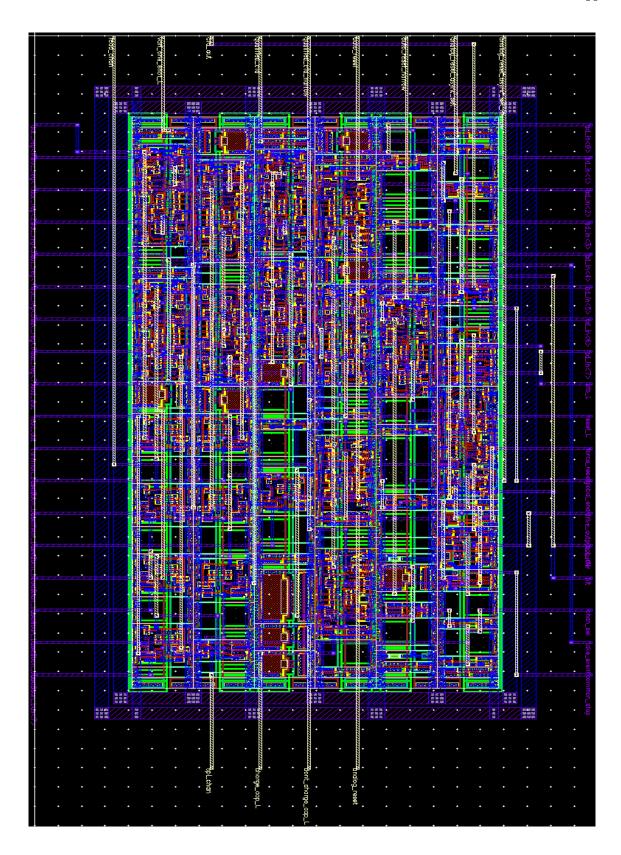

| 5.2    | Layout of the HINP signal channel digital logic generated by the        |      |

|        | place n route tool                                                      | 59   |

# LIST OF TABLES

| Table |                                                   | Page |

|-------|---------------------------------------------------|------|

| 3.1   | Bit assignments of configuration register 0       | 34   |

| 3.2   | Bit assignments of configuration register 1       | 35   |

| 3.3   | Bit assignments of configuration register 2       | 36   |

| 3.4   | Modes of Operation                                | 39   |

| 3.5   | Modes of Operation Continued                      | 40   |

| 3.6   | Truth Table of Priority Encoder                   | 44   |

| 4.1   | Bit assignments of DAC register in signal channel | 53   |

### CHAPTER 1

#### INTRODUCTION

This chapter is intended to introduce the reader to the subject of radiation monitoring and will describe how custom multi-channel integrated circuits are useful in the detection and measurement of ionizing radiation. The IC (Integrated Circuit) outlined in this thesis, called HINP5 (Heavy-Ion Nuclear Physics- Version 5), is the newest chip in our research group's CMOS (Complementary Metal-Oxide Semiconductor) ASIC (Application Specific Integrated Circuit) "tool box" for radiation detection. The ICs in the "tool box" are being developed by the IC Design Research Laboratory at Southern Illinois University Edwardsville (SIUE) in alliance with researchers from the Nuclear Reactions Group at Washington University in Saint Louis (WUSTL).

## 1.1 Research Background

The IC Design Research Laboratory at SIUE in collaboration with the Nuclear Reactions Group (Department of Chemistry) at WUSTL have been working, since 2001, to develop a class of multi-channel custom integrated circuits (ICs) useful for researchers engaged in various nuclear physics experiments where the identification and measurement of ionizing radiation is required. Usually in these experiments, the position of interaction within the detector must be precisely estimated, the particle energy must be measured, and the relative time of arrival of the particle must be determined.

The groups first achievement was an analog shaped and peak sensing chip. It had on-board CFD (Constant-fraction Discriminators) and sparsified readout. It is known as HINP (Heavy-Ion Nuclear Physics). The chip was designed for use with Si-strip detectors. The second chip, called PSD (Pulse Shape Discrimination), was designed

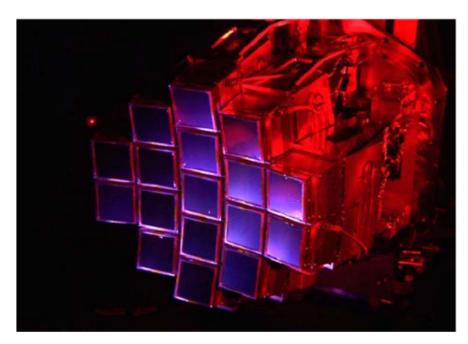

to complement the HINP chip logically in terms of being able to support different detector types. PSD8C is used with scintillators and uses almost the same supporting hardware as does HINP. This thesis is devoted to describing the digital logic contained within the latest generation HINP chip known as HINP5 (HINP Version 5). A typical array of silicon strip detectors is shown in Figure 1.1.

Figure 1.1: An array of si strip detectors

A Si-strip detector can be defined as a reverse-biased p-n junction diode. When the radiation energy or the charged particles are detected, a packet of electron-hole pairs are generated in the detection material. The number of electron-hole pairs depends on the energy of the particle and on the material it passes through. The charge packet size is proportional to the energy of the incident radiation. Each of the 17 (blue-shaded) panels, shown in the Figure 1.1, consists of 32 detectors (16 placed horizontally and 16 vertically).

This is useful in identifying the position where the particle struck. For the purpose

of identifying position, two silicon detectors of differing thickness are used (65  $\mu m$  and 1.5 mm). The 65  $\mu m$  detector is single-sided with silicon strips in the vertical direction while the 1.5 mm detector is double-sided with silicon strips that are vertical in the front and horizontal on the back.

## 1.2 HINP IC

As already discussed, HINP5 stands for Heavy Ion Nuclear Physics - Version 5 and is a 16-channel chip. HINP5 is a multi-channel chip which generates sparsified analog pulse trains for both timing information (in respect to an external reference) and for linear (pulse height) information. HINP5 is the latest version of the earlier HINP chips. HINP5 is a custom intergrated circuit that posses some special features which no commercial IC possesses. Special features of HINP5 are:

- Sixteen(16) independent channels

- Has two different modes operating in parallel: low-gain mode (400 Mev full-range) and high-gain mode (100 Mev full-range)

- Fast analog multiplicity and channel OR output to help in making decisions about whether to readout or not

- Auto-reset capability allows for data sparsification

- Supports both negative and positive polarity pulses

- Built-in time-to-voltage converters supporting 250 nsec and 2  $\mu sec$  full-scale ranges

- Has on-chip CFDs (Constant Fraction Discriminators)

- Better noise performance(<25 keV)

### • Can also be used with external charge amplifier

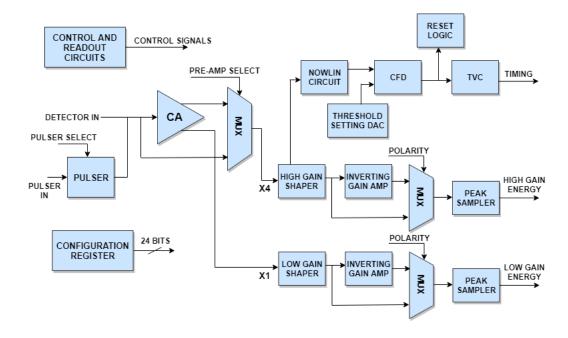

The architecture of a single HINP5 channel is shown in Figure 1.2. Each of the HINP channels consists of the following primary blocks: charge amplifier (CA), a pair of slow shapers, a pseudo-constant fraction discriminator (CFD), a pair of peak samplers, and a time-to-voltage converter (TVC). The signal channels also contains some bias circuits, reset logic, and digital readout electronics.

The HINP5 chip is designed using the AMS 0.35  $\mu m$  CMOS process. This CMOS process supports 4 metal (Metal 4 is an extra thich metal layer) and 2 polysilicon layers. Designers using this process have access to both 5 V (PMOSM, NMOSM) and 3.3 V (PMOS, NMOS) FETs, Bipolar Junction Transistors (BJTs), and two kinds of resistors implemented using the POLY 2 layer. One is RPOLYH (lightly doped POLY 2 layer) and the other is RPOLY2 (heavily doped POLY 2 layer). The designer also has access to double poly capacitors (CPOLY). In the design described in this thesis, 3.3 V FETs (PMOS,NMOS) are used which are faster (and smaller) than the 5 V FETs. The minimum length of the 3.3 V FETs is 0.35  $\mu m$ .

As shown in Figure 1.2, HINP5 consists of three major blocks: linear circuits, timing circuits, and the configuration/readout circuits. In the next section we will briefly describe operation of a HINP5 signal processing channel.

#### 1.2.1 Linear circuits

The first element in the linear block is the charge amplifier (CA) and it is designed to have two outputs: high-gain (charge gain of x4) and low-gain (charge gain of x1). Additionally, one can also utilize an external preamplifier. The purpose of the CA is to amplify the input charge packet either by a gain of 1 (low-gain) or by a gain of 4 (high-gain).

Figure 1.2: Block diagram of typical HINP5 channel [Korkmaz, 2019].

The two outputs (currents) from the CA are the inputs to a pair of slow shapers (Gaussian low-pass filters). The low-gain shaper output is linear to 400 MeV while the high-gain shaper output is linear to 100 MeV. Each of these sub-channels generate sparsified analog pulse trains along with synchronized addresses for digitization by an off-chip analog-to-digital converter (ADC) [Sadasivam, 2002].

Since it is the peak voltage at the output of the pulse shaper which is proportional to the detected particle energy, the outputs from the two shapers are presented to a pair of peak-samplers before being sent off-chip to be digitized by the ADCs. The input to the slow shaper is a charge packet. The peak sampler was designed to find only negative peaks, so depending on the polarity (*i.e.* electron or hole collection) the output from the shaper may be inverted prior to peak detection.

## 1.2.2 Timing circuits

The timing circuits are responsible for the accurate measurement of the time elapsed between the particle striking the detector and an external time reference provided to the chip. The major components of the timing branch are the CFD (Constant Fraction Discriminator) and the TVC (Time-to-Voltage Converter).

The initial op amp in the pulse shaper is frequently referred to as a CSA (Charge-Sensitive Amplfier) since it converts the input charge packet to a voltage. The output of this CSA amp is then fed to the CFD which generates a logic signal that marks the arrival time of the particle/radiation at the detectctor [Orabutt, 2019]. The use of a CFD guarantees that the arrival time is not a function of particle energy.

The CFD consists of a leading-edge discriminator (*i.e.* analog comparator) and a zero-crossing discriminator. The leading-edge discriminator must transition first and is used to qualify the zero-cross output which sets the timing. The logic high output from the CFD indicates that the channel has been hit. The use of a Nowlin circuit ensures that the timing signal is independent of particle energy.

This CFD (digital) output signal starts a temperature-independent current, which in turn charges a capacitor in the TVC. Reiterating, the TVCs (one per channel) start when they receive the signal to start from their respective CFD and stop when an externally generated timing reference (common to all channels) is applied. The time when the channel was hit relative to the common stop signal is proportional to the voltage across the TVC capacitor.

#### 1.2.3 Configuration and readout circuits

The HINP5 IC has both digital control and analog circuits (that provide proper biasing for the channels) in the central common channel. The common channel also contains the configuration and readout circuits. These circuits configure the HINP5 chip. The readout circuits provide data in the form of three analog pulse trains (high-gain peak voltage, low-gain peak voltage, and the TVC voltage) along with synchronized digitally encoded channel addresses to the off-chip ADCs and FPGA (Field Programmable Gate Array) logic.

As shown in the Figure 1.2, the configuration circuitry consists of three 8-bit registers that can be loaded selectively to generate various control signals. The control signals generated by the configuration registers are capable of setting the Nowlin delay, setting Nowlin mode (short versus long), adjusting the AGND (signal ground) voltage, selecting even channels or odd channels for pulsing, and selecting TVC measurement range. The TVC can be switched between the two ranges: 250 ns full-scale and 2  $\mu s$  full-scale. The biasing, configuration, and the readout circuits are positioned at the center of the chip.

#### 1.3 Previous Work

The fundamental architecture of the HINP chip has remained relatively unaltered over the span of many design revisions until recently being significantly changed. The first HINP IC designed had 16 signal channels. It was called HINP16C and unfortunately was never used in experiments due to a design error. It had design issues such as poor linearity and poor noise performance. The revised HINP IC, HINP2, with 16 channels was used in many experiments using the HiRA (High Resolution Array) Si array had two internal CSA (Charge Sensitive Amplifier) gain modes. The modes were referred to as high-gain (dynamic range of 400 MeV) and low-gain (dynamic range of 100 MeV). The gain modes could **not**, however, be used at the same time. It had a shaper with a fixed peaking time of 1.2  $\mu$ s, and each channel possessed a TVC with two time ranges: 250 ns and 2  $\mu$ s.

HINP3 (version 3) had a few additional features such as a shadow register, and the

fast shaper circuit in the CFD module was modified to make it programmable. The addition of the shadow register helps users to determine which channels have been hit prior to readout whereas the modification of the fast shaper circuit allows users to select one of two time constants. The HINP3 IC displayed considerably better performance in terms of both linearity and energy resolution *i.e.* the internal CSA gains were 30% greater compared to the HINP2 design. The timing performance of HINP3 was also proven to be better along with the additional features. But unfortunately the changes made to integrate the shadow register into the design affected the auto-reset circuit which makes the data sparsification feature of the chip possible.

Later, HINP4 (version 4) was fabricated to correct the problem with the auto-reset circuit, increase the dynamic range properties and also to remedy some of the issues identified with the on-chip TVC circuits. In HINP4, even though some of the channels displayed good linearity, some (random from chip to chip) of the other channels suffered from linearity issues. The version 5 IC, detailed within this thesis, is designed to achieve even better performance than its antecedents in terms of linearity and noise. This thesis describes in detail the digital configuration and readout electronics implemented in the HINP5 chip.

#### 1.4 Object and Scope of Work

The object of this thesis work is to design the readout and configuration circuits for HINP5. HINP5 is intended for use in the detection and measurement of ionizing radiation in instruments used for experiments in low- and intermediate-energy nuclear physics and for researchers working with radioactive ion beams. HINP5, like the earlier versions, is an analog shaped and peak sensing chip used with arrays of Si-strip detectors.

There are five chapters in this thesis. Chapter 1 has a brief introduction about the

evolution and architecture of the HINP IC. In Chapter 2, we will describe the overall system-level design. In particular, the chipboards upon which the HINP chips reside along with the motherboard that the chipboarbs are plugged into will be discussed. A discussion of how the HINP chip interfaces to the chipboard FPGA. Chapter 3 describes in detail the digital circuits which reside in the common channel of HINP5. In Chapter 4, the digital logic contained within an individual signal channel is described in detail. Finally, Chapter 5 will provide a summary of the work done so far, and describes the future work that needs to be done on HINP5.

This thesis focuses only on the design of the digital configuration and readout electronics residing on HINP5. Details about the linear branch circuits in HINP5 are covered in another thesis [Korkmaz, 2019], and the details on the timing branch of HINP5 are discussed in yet a third thesis [Burla, 2019]. An earlier thesis describes the CFD related circuits [Orabutt, 2019].

#### CHAPTER 2

#### SYSTEM LEVEL DESIGN

#### 2.1 Introduction

In this Chapter we will discuss the Field Programmable Gate Array(FPGA) and its design which directly interfaces to the HINP5 ICs. Before going into details about the FPGA design, there is a need to understand the system level design where the FPGA interacts with a motherboard, two HINP chips and several ADCs. Bold-faced words in this chapter correspond to signal names.

## 2.2 System Operation

The HINP5 chip generates analog pulse train outputs for both timing and energy along with synchronized digitally encoded channel addresses. There is a need to digitize the analog outputs using an external Analog to Digital Controller (ADC). The reason for digitization is that transmitting high resolution analog data is prone to degradation due to environmental noise where as transmitting the digital data is less prone to loss when transmitted over significant distances.

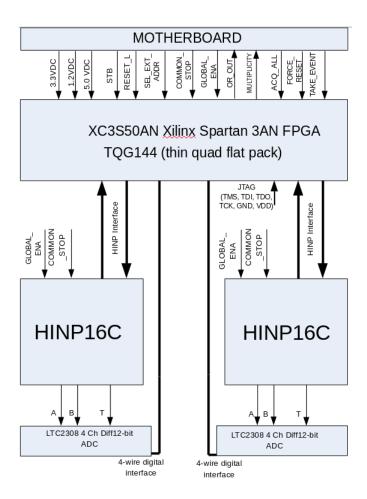

The chipboards (CBs), which in turn plug into the motherboard (MB), are designed so that the analog outputs from the HINP5 chip are digitized locally. The chipboard contains two HINP5 ICs, a Spartan 3A Xilinx FPGA, three ADCs, and a small amount of support circuitry. The Xilinx Field Programmable Gate Array (FPGA), shown in the Figure 2.1 supports two 8-bit PicoBlaze micro-controllers. The PicoBlaze is a softcore provided by Xilinx and must be programmed in assembly language but uses relatively little resources on a Spartan3A FPGA. The analog pulse trains produced by the HINP chip are digitized by the LTC1865 ADC manufactured by Linear Technologies.

The FPGA interfaces with the ADCs via a 4-wire digital interface. The 4-wire digital interface consists of **SCLK** (serial clock), **SDI** (serial data in), **SDO** (serial data out) and **CONV** (start conversion). The analog data from both of the HINP chips is simultaneously digitized and stored in the FPGA memory.

The Xilinx FPGA contains a two-port shared Random Access Memory (RAM). The two PicoBlazes share the memory. The motherboard acquires data from the FPGA by issuing four acquisition clocks per channel. On the first clock the chip ID and channel address will be read out. On succeeding clock pulses the ADC data for the **A**, **B**, and **T** values will be read out where **A** is the high gain pulse shaper output, **B** is the low gain pulse shaper output. The digitized data(**A**, **B**, and **T**) stored in the FPGA memory is sent to the motherboard and then transferred to the XLM.

Figure 2.1: Block Diagram of the System

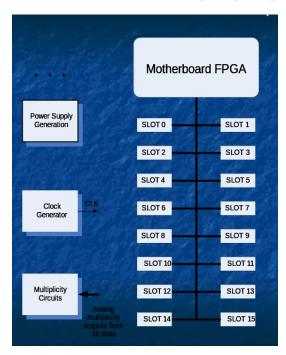

## 2.3 MotherBoard

The motherboard (MB) has sixteen slots. The CBs, briefly described in the previous section, plug into these slots. Hence, a single MB can services 512 Si-strip detectors. The power supply generation block on the MB is capable of generating 1.2 V, 3.3 V and 5 V. The supply voltages 1.2 V and 3.3 V are distributed to the HINP CBs.

The multiplicity circuits on the MB recieve analog multiplicity outputs from the sixteen slots. Multiplicity outputs are analog voltages proportional to the number of channels which have been struck by radiation. Each HINP5 chip in the system produces a multiplicity output. Everytime a channel is "hit", the multiplicity output goes up by approximately 100 mV. If all sixteen channels on the HINP chip have been hit then approximately 1.6 V is observed on the multiplicity output pin [Orabutt, 2019].

Figure 2.2: Block Diagram of the MotherBoard

The MB generates a master clock (STB) inside the motherboard FPGA and

a master reset (RESET\_L). They are reproduced and used by the FPGA on the chipboard. The TAKE\_EVENT, ACQ\_CLK, and ACQ\_ACK signals are used to acquire ADC data. The global enable (GLOBAL\_ENA) signal enables the sixteen channels of the HINP chip globally. If the bit is set (GLOBAL\_ENA = 1) then all of the channels in the HINP chip are enabled. In addition, each channel has its own channel register which enables/disables that particular channel. The channel OR (OR\_OUT) and MULTIPLICITY signals are sent to the MB. These signals indicate if any of the channels have yet to be read out. The reset signals: FORCE\_RESET and RESET\_L signals are asserted from the motherboard. RESET\_L is a master reset signal which is active low and FORCE\_RESET when active resets all the signals. This is done usually after the data acquisition process has completed. In Figure 2.3, a chipboard is plugged into one of the sixteen slots on the motherboard.

Figure 2.3: Chipboard connected to one of the 16 slots on motherboard

## 2.4 Chipboard FPGA

As already discussed, two HINP chips along with an FPGA and some support circuitry reside on the system chip boards (CBs). In this section, we will briefly describe the FPGA which is used on the CB.

A FPGA (Field Programmable Gate Array) can be defined as a Integrated Circuit (IC) which provides designers with programmable logic blocks and memory blocks (on-chip storage, RAM, PROM) etc. We use a Xilinx Spartan-3AN FPGA in our design.

The Spartan-3AN FPGA supports non-volatile RAM storage, which is capable of storing the configuration data of the FPGA. A JTAG interface is used to program configuration data into the FPGA. The Spartan-3AN is a very cost-effective non-volatile FPGA solution. The other key features of the Spartan-3AN FPGA are [DS5, 2014]:

- Parallel NOR Flash configuration

- SPI serial Flash configuration: uses either the Atmel DataFlash architectures or STMicroelectronics

- Parallel NOR and SPI serial Flash PROMs supports MultiBoot FPGA configuration

- Embedded 8 bit PicoBlaze controller & 32 bit MicroBlaze processor

- Memory interfaces (DDR supported)

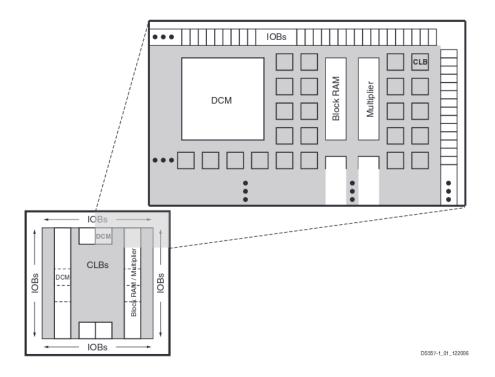

Figure 2.4 shows the 5 basic programmable logic elements of the Spartan-3AN architecture.

• CLBs (Configurable Logic Blocks) that performs logic

- and storage blocks say Latches or Flip-flops using LUTs (Look up Tables).

- Block RAM, has dual port of 18 kbit for data storing purposes,

- Muultiplier Blocks,

- IOBs (Input/Output Blocks), used to interface with external devices also includes DDR registers supporting high transfer rates.

- DCM(Digital Clock Manager) provides multiplying, delaying, phase-shifting and dividing clock signals etc [DS5, 2014].

Figure 2.4: Spartan 3AN Architecture

## 2.5 PicoBlaze Soft Core

The PicoBlaze is an 8-bit micro-controller with a Reduced Instruction Set Computer (RISC) architecture. Its core is optimized for Virtex II, Spartan 3, Virtex II pro FPGA

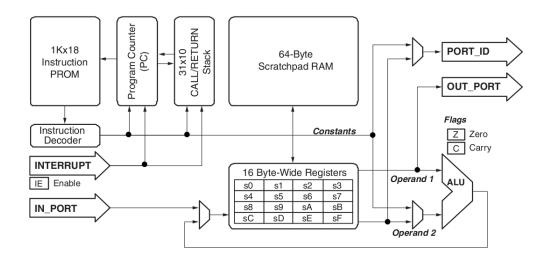

families [UG1, 2008]. It is completely embedded into the target FPGA and does not require any external resources. It is extremely flexible and can interface to additional FPGA logic via its I/O (Input/Output) ports. The PicoBlaze micro controller is a good fit for this application, as it is compact and consumes less resources on the FPGA when compared to other 8-bit micro-controllers available in the market. The controller is programmed in assembly language. A PicoBlaze supports the following features [UG1, 2008]:

- General purpose registers of 16 byte long for data

- 64 Byte internal scratchpad RAM (Random Access Memory)

- 1024 Instruction PROM (Programmable Read Only Memory)

- Can be expandable with 256X256 I/O ports

- 8 bit Arithmetic Logic Unit (ALU); provided Zero and Carry flags

- Automatic CALL/RETURN stack memory with 31 locations.

- Fast interrupt response

- Assembler with simulator that supports instruction set

A block diagram of the PicoBlaze micro-controller is shown in Figure 2.5, It has sixteen general purpose registers, designated as s0, s1, and so on through sF. All the registers are similar with none of them reserved for special operations and has no priorities set.

The PicoBlaze also has an internal 64 byte scratchpad RAM, addressable directly (with immediate constants) or indirectly from the register file (using the register contents) through **FETCH** and **STORE** commands. The **FETCH** instruction reads

Figure 2.5: PicoBlaze Embedded Microcontroller

any of the memory location of 64 byte scratchpad RAM into any of the available 16 registers whereas the (STORE) instruction writes/copies the contents from any of the registers to any of the 64 available memory locations.

The PicoBlaze has a 1K PROM block, as shown in Figure 2.5, capable of executing 1024 instructions where each instruction is 18 bits long. These instructions are compiled using the PSM assembler and then loaded automatically during the configuration process of the FPGA. The PicoBlaze supports a maximum space of 1K (1024) instructions of code (000-3FF). The default behavior of the PC can be altered by the CALL, JUMP, RETURN, Interrupt, RETURNI and the reset operations.

The 8-bit ALU present within the controller is capable of performing basic arithmetic and logical operations like addition, subtraction, comparisons, bit-wise tests, AND, OR, XOR, as well as rotate and shift operations affecting the **Carry**. In case the **INTERRUPT\_ENABLE** flag is set, then the **INTERRPUT** input is enabled. The PicoBlaze does not have an accumulator. Instead, the first operand (address) of the instruction points to the register which will store the result.

The PicoBlaze has an automatic reset event. Once the FPGA configuration is complete, it resets the value of the PC to address 0, disables the interrupts, clears all the flags *etc.*, but the scratchpad RAM and data registers are not affected by this reset event. The PicoBlaze micro-controller is expandable as it supports 256 Input and 256 Output ports. This allows the processor to interface to external peripheral devices or other FPGA logic.

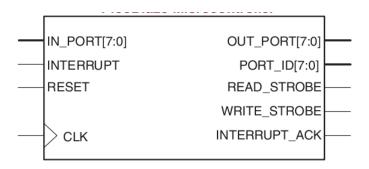

Figure 2.6: PicoBlaze top-level Interface Connections

Figure 2.6 shows the top-level interface signals of the PicoBlaze micro-controller:

- PORT\_ID (8-bit long) that outputs the port address,

- IN\_PORT (8-bit data line) that hold the data during an input operation where data is read from this port to the specified register (sX) on the rising clock edge if the READ\_STROBE is set,

- OUT\_PORT (8-bit data line) holds the data for 2 clock cycles during output operations where the controller writes the data (contents of the register, sX) to this port if WRITE\_STROBE is set,

- **RESET** (1-bit input) signal set to high for one clock cycle resets the PicoBlaze controller automatically following the FPGA configuration,

- **CLK** signal where all the PicoBlaze synchronous components are clocked with rising clock pulses

- INTERRPUT\_ENABLE flag set then generates an

- INTERRUPT by setting this input for at-least 2 clock cycles, and if

- INTERRUPT\_ACK is set notifying that the INTERRPUT event happened and the signal is set during the second clock cycle of the two-cycle interrupt.

## 2.6 HINP Interface

As discussed in the previous sections, each of the two PicoBlaze micro-controllers in the FPGA are programmed to control one of the two HINP5 chips on the chipboard. The PicoBlaze microcontrollers in the FPGA are programmed to configure both the HINP5 chips and for acquisition of the analog pulse trains produced by the timing and linear branches of HINP5. The HINP interface shown in Figure 2.1 consists of a set of signals helpful in performing the various configuration and readout tasks.

The FPGA writes data into the address and configuration registers present inside the common channel of the HINP5 chip. When the **WRITE** signal is made HIGH, the address and mode information is loaded into the address register on the rising edge of **STB** and configuration information is loaded into either the configuration registers or the DAC registers on the falling edge based on the mode selected during the rising edge. The data to be written is available on the 8-bit **AD** bus. **AD** is a bidirectional bus which allows an user to input data into the HINP5 chip and output data from the chip. The strobe, **STB**, is generated by the FPGA's PicoBlaze.

During the readout process, the FPGA reads the address of the channel from the HINP chip that is being processed, and it also monitors the **OR\_OUT** output from

the HINP chip. The **OR\_OUT** is high when at least one channel on HINP has been hit. After all channels have been read out the **OR\_OUT** will return to the low state.

Using the ACQ\_ALL signal, asserted from the motherboard, one can force the acquisition of all the sixteen channels on chip. One can also select a particular channel for data acquisition by giving the channel address on the bus externally when the SEL\_EXT\_ADDR pin is asserted from the motherboard. The HINP chip receives the COMMON\_STOP and GLOBAL\_ENA signals directly from the motherboard. When the COMMON\_STOP is brought high, the TVC (Time to Voltage Converter) in each of the sixteen channels will halt. GLOBAL\_ENA enables setting of the hit registers. The readout electronics will be described in more detail in Chapter 3 and Chapter 4.

## 2.7 Analog-to-Digital Converter

The chipboards use the Linear Technology's LTC1865 Analog to Digital Converter (ADC). It is a 16-bit Analog-to-Digital converter with a programmable 2 channel MUX (Multiplexer, enabling it to operate in either the single-ended or differential mode [ADC, ]. The conversion starts with the CONV signal going high and waits for some time (t\_conv) to finish the conversion. After the conversion completes, the ADC goes into sleep mode (just draws leakage current). A low on the CONV pin enables the SDO pin and data is shifted out. The ADC converts analog data to digital and that data is then transferred serially, synchronized to a clock, SCK. The SDI and the SDO are the serial input and serial output data pins. Configuration bits are shifted into the ADC and digital data is shifted out.

The ADC has two analog channels (CH0, CH1) The inputs to these channels need to be noise-free respective to GND. The first two bits of the SDI input sequence will configure the MUX as illustrated in the table below.

|              | MUX ADDRESS |          | CHAN | NEL # |     |

|--------------|-------------|----------|------|-------|-----|

|              | SGL/DIFF    | ODD/SIGN | 0    | 1     | GND |

| SINGLE-ENDED | 1           | 0        | +    |       | _   |

| MUX MODE     | 1           | 1        |      | +     | -   |

| DIFFERENTIAL | 0           | 0        | +    | -     |     |

| MUX MODE     | 0           | 1        | -    | +     |     |

|              |             |          |      |       |     |

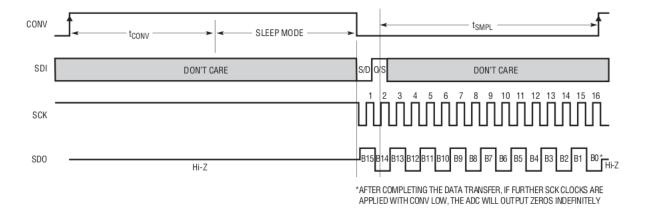

Figure 2.7: Channel Selection Bits in LTC1865

As discussed above, the LTC1865 ADC starts conversion on the rising edge of the CONV. When the CONV signal goes low, the 2-bit data is clocked into the SDI pin on the rising edge of shift clock, SCK. Additional data bits clocked in on the SDI pin are ignored until the next CONV cycle. The LTC1865 supports full-duplex mode, where receiving and transmitting data is done simultaneously [ADC, ]. As shown in Figure 2.8, the data transfer is synchronized with SCK where each bit is transmitted on the falling edge of SCK and received on the rising edge of SCK in both receiving and transmitting systems. After the completion of the data transfer, if one continues to apply clock pulses with the CONV signal low, then the SDO outputs zeros endlessly.

Figure 2.8: Operating Sequence Diagram

#### CHAPTER 3

#### COMMON CHANNEL

The HINP5 IC is made up of sixteen signal processing channels and a single common channel placed in the center of the chip. The common channel in HINP5 contains the digital configuration and readout logic as well as the analog bias circuits that are common to all sixteen signal channels. The common channel contains analog circuits such as the "Power on Reset" (POR) circuit which generates an active low reset pulse which is guaranteed to be at least 2  $\mu sec$  long when HINP5 is first powered up. This POR signal is used to start a PTAT (Proportional-to-Absolute-Temperature) current generator which provides a 11.5  $\mu A$  bias current to each of the 16 signal channels [Orabutt, 2019].

An analog "signal ground" generator circuit provides an analog signal ground (AGND). AGND is generally set at a potential halfway between the AVDD and AVSS rails. This signal ground is used in the analog circuitry in the signal channels as well as by the off-chip single-to-differential buffers located in the common channel. The nominal AGND reference voltage is around 1.65 V and can be trimmed using 3 configuration bits.

Each signal channel contains an auto-reset circuit which produces a reset signal after a programmable delay defined by 4 configuration bits. The configuration bits are used to select one of 16 currents (logarithmic distribution) which is then used to discharge a capacitor in the auto-reset circuit located in the signal channel. The auto-generated reset signal resets the hit register along with the TVC and peak detector circuits in each of the the sixteen channels if readout is not initiated within the "wait" time (delay that is selected via the configuration register). The circuit

which generates the current used by the auto-reset circuit is located in the common channel.

Analog circuits are also located in the common channel which buffer the analog multiplicity signal as well as single-ended-to-differential buffer circuits which are used to drive the low-gain, high-gain, and TVC analog pulse trains off the chip in a differential manner. The LTC1865 expects differential input signals if high performance is required, as is the case in our application.

In the remainder of this Chapter, we will only discuss the digital configuration and readout circuits which reside in the common channel. Digital circuits residing in the signal channel will be covered in Chapter 4 of this thesis.

## 3.1 Digital Design Using EDI Tools

The design of the configuration and readout electronics was accomplished using a Verilog driven design style. The design was carried out using Cadence's EDI (Encounter Digital Implementation) tools. These tools give designers a way to simulate, synthesize, then and place n 'route their Verilog driven designs.

#### 3.1.1 Why Standard Cell Design

All the digital circuits discussed in this thesis are implemented using a standard cell library because the standard cell design speeds up the design phase of digital circuit design [Eriksson et al., 2019]. Use of this approach also makes it much easier to modify a design when an error is identified or a feature must be added. This advantage is very important in our application. After making a change to the Verilog source code, it only takes a few minutes to re-generate the physical layout of our circuits.

The standard cell design methodology uses pre-designed and pre-tested logic cells from the digital standard cell library in the 0.35 micron AMS design kit (HITKIT)

as the building blocks. Since the standard cell approach requires much less design effort compared to full-custom layout, more time can be devoted to testing. In custom layout design, most of the primitive cells are designed from scratch, leaving an opportunity to choose arbitrary alignment, flexible sizing of the transistors, high degree of optimization in terms of area, etc. but the standard cell design approach is generally recommended for designing digital circuits as the custom layout design methodology is very slow, tedious, and takes more design effort.

## 3.1.2 Standard Cell Design Flow

Unlike custom design, rather than drawing schematics for the design using a schematic editor, the standard cell design flow usually starts with the designer creating a generic schematic of the digital logic to be implemented. The generic schematics created are used to clearly define the logic that needs to be designed. The schematics can then be described using a HDL (Hardware Description Language).

The behavioral description of the digital logic described by the generic schematics must be coded using either Verilog or VHDL. Verilog is almost exclusively used in IC design and so the HINP5 digital logic is described using Verilog. A SystemVerilog (a modern, more feature laden version of the Verilog language which is generally used for creating testbenches) test fixture needs to be created to test if all the circuits designed function properly. Our test fixture consists of three parts: a SystemVerilog task file that has various system level tasks defined in it for verification, a local parameters file that holds the list of parameters that drive specific tasks and a SystemVerilog testbench that instantiates the design and then applies test vectors to the design.

In addition to the design and test fixture files, we needed to create an "environment file" called *env.tcl* for each of our digital designs. The *env.tcl* file is one of the Tcl (Tool Control Language) scripts from the tool box written by Dr. Engel and his

graduate students here at SIUE to ease the usage of the EDI computer design tools. The *env.tcl* file specifies the design parameters to be set when performing simulations, synthesis, and place n' route.

Examples of things which are specified in the *env.tcl* file include simulation mode (register transfer language description, synthesized netlist, place n' route netlist), basename, list of RTL Verilog files, list of synthesis files, VCD (Value Change Dump) signals, place n' route flow specifications, *etc*. Simulation mode can be set to either *rtl*, *syn* or *pnr*. The basename should be set to the design name which one is working on, and place n' route flow specifications are items such as floorplanning options, spacing between core and boundary, which router to be used for routing, pin placement around the core boundary, *etc*.

One begins by running a behavioral-level simulation of the design. We use the EDI tool NC-Sim for simulation and then SimVision for visualization. One sets the simulation mode to "rtl" in the env.tcl file and then types the command sim in the Linux command window to invoke the Tcl (Tool Control Lanuage) script, called sim.tcl from the tool box. See section E.1 of Appendix E. One then analyzes the simulation results in order to verify that the behavioral description of the circuit functions properly. No delays are included in a behavioral simulation.

After verifying the behavioral description of the circuit, logic synthesis of the behavioral design has to be done using a design compiler which converts Verilog described behavioral models into gate-level netlists. The design compiler in the Cadence EDI toolset is called *RTL Compiler*. This synthesis tool selects cells from the AMS standard cell library. The digital standard cell library provided in the AMS design kit has around 200 standard logic cells.

A SDC (Synopsys Design Constraints) file must be created which specifies the design and timing constraints, for example, clock constraints, IO (Input/Output)

timing constraints, timing exceptions, *etc*. Most digital designs have one or more clocks and the SDC file specify the frequencies of these clock signals. In the SDC file one can tell the tool that the clock has, for example, a 50 % duty cycle and a period of 100 ns.

One then synthesizes the behavioral description by typing the command syn in the Linux command window to invoke a Tcl script, called syn.tcsh. See section E.2 of Appendix E. A gate-level Verilog netlist of the Verilog description is generated. We then run a simulation of this synthesized design again but with simulation mode specified as "syn" this time in the env file. Finally, one analyzes the simulation results to verify that the design functions correctly. Now the delays of the components/logic cells are seen but not wire delays.

Before running the place n' route tool, one specifies the parameters related to floor planning, power planning, cell placement, etc. in the env.tcl file. Floor planning includes providing the dimensions of the core, the aspect ratio, the cell utilization factor, the distance between the core and the boundary, pin assignments, spacing between the pins, metal layers to be used, etc. Power planning includes setting the width of the metal as well as the separation between the rails, metal layer to be used for rails, and more.

One then types the command pnr in the Linux command window to run a Tcl script, called pnr.tcsh. See Section E.3 of Appendix E. The Encounter Place n' Route tool in the EDI toolsuite generates a Verilog netlist. During the process of place n' route, the complete layout generated is verified to check if there are no geometry and connectivity errors. Finally, we run the simulation again with simulation mode set as "pnr" this time in the env file and verify that there are no timing issues in the simulation results. In addition to wire delays, there will also be delays from the buffers that are incorporated during clock tree synthesis.

We are now able to export a layout and a schematic from the EDI tools to Cadence Virtuoso (the custom IC schematic and layout tools). To do this, we simply run two commands edi2ic and edi2sch in the Linux command window which invokes the Tcl scripts, called edi2ic.tcl and edi2sch.tcl. See section E.4 of Appendix E. For a complete description of the flow, the interested reader should refer to sections 9, 10 and 11 in the ECE484 Lab Manual [G.L.Engel, 2018]. We must export our digital designs to the custom layout tools so that they can be connected to the analog modules which were created using the custom layout and schematic entry tools.

Once the design has been exported to Virtuoso, it is necessary to perform Design Rule Checks, more commonly known as DRCs. Here we check the layout against a set of foundry supplied design rules. DRC is the step taken to ensure that the design is "manufacturable". One then must run a LVS (Layout Versus Schematic) check that compares the netlist extracted from layout with the netlist created from the schematic. LVS checks ensure that the schematic and layout agree with one another.

It is now possible to run electrical simulations of the digital logic. To make this possible, the standard cell design which was imported into Virtuoso is driven by a Verilog A module instantiated in the Virtuoso testbench. The Verilog A module in turn instantiates a series of PWL (Piece-Wise-Linear) voltage sources, one for each if the digital inputs in the design.

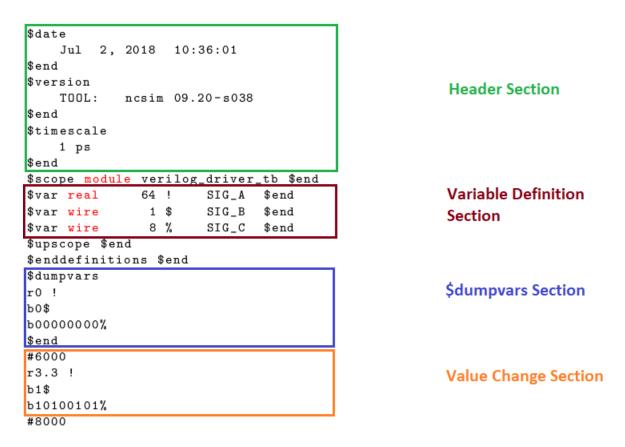

The Tcl script  $make\_vcd.tcl$  generates the Verilog code which is used to create the a (Value Change Dump) file. This code must be included in the SystemVerilog testbench prior to running the simulation. The VCD file created when the simulation is run contains a record of all changes in the digital input signals. Figure 3.1 [Orabutt, 2019] contains a sample VCD file.

A python script (vcd2pwl) then converts the VCD dump file to a series of piecewise linear files. The  $make\_vcd.tcl$  script automatically creates the VerilogA module

described above. The user only needs to create a symbol for the VerilogA module before it can be instantiated into the Virtuoso testbench. The rise/fall times, scale factors and logic levels for the analog signals can be specified in the python script. See section F.2 of Appendix F. The standard PWL file format is a time-voltage pair separated by space.

Figure 3.1: An example of a VCD file

# 3.2 Configuration and Readout Electronics

The configuration and readout electronics provide control for all sixteen signal processing channels. The common channel has three 8-bit configuration registers which supports 24 configuration bits in total. These configuration registers are selectively loaded to configure the HINP5 chip. The readout circuits allow for the analog pulse trains along with there synchronized digital channel addresses to be transmitted to the FPGA on the CB.

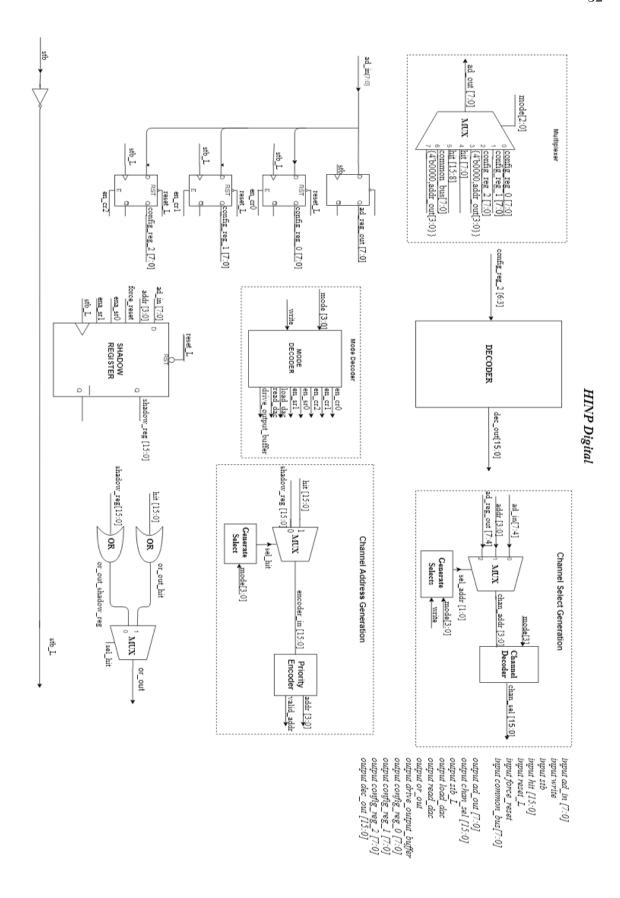

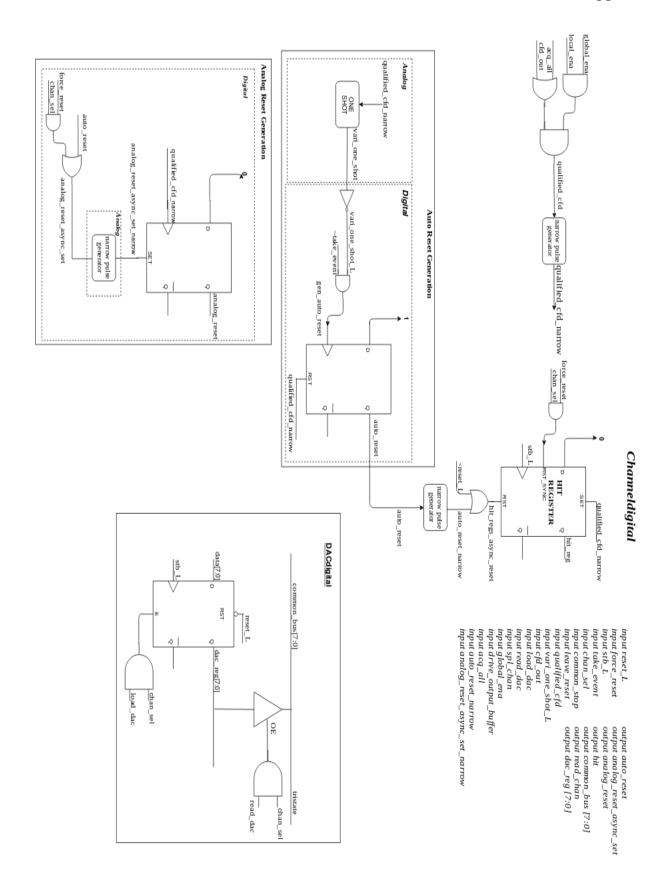

As shown in Figure 3.2, the common channel digital circuits (configuration and readout) consists of an address register, three 8-bit configuration registers, a 16-bit shadow register, mode decoding circuitry, OR generation, a 4-to-16 decoder, and channel address/channel select generation circuits.

Note: Any bold-faced word in this chapter corresponds to the signal name in the Verilog code of that particular module. The full Verilog description of the digital modules discussed in this chapter can be found in section A.1 of Appendix A.

## 3.2.1 Address Register

The address register is an 8-bit register, **ad\_reg**, in the common channel that is used to register address and mode information on the rising edge of **stb**. This register resets asynchronously the on falling edge of **reset\_L** which is the master reset signal for the HINP5 chip. The lower nybble contains the **mode** and the upper nybble the **address**.

$$ad\_reg \leftarrow \{address, mode\} \tag{3.1}$$

The address and mode information which is loaded into **ad\_reg** comes from an 8-bit wide **ad\_in** bus. The address register is a positive edge-triggered D-register

Figure 3.2: Generic schematic of logic that resides in the common channel

which is clocked by **stb** and asynchronously reset when the master reset (**reset\_L**) signal goes low.

## 3.2.2 Configuration Registers

There are three 8-bit configuration registers **config\_reg\_0**, **config\_reg\_1**, and **config\_reg\_2** located in the common channel. The enable signal of the specified configuration register is active when that particular register address and mode is selected. The data present on the 8-bit wide **ad\_in** bus will be loaded into that designated register on the falling edge of the **stb**. As the standard cells library contains only a positive edge triggered register, the configuration registers are clocked with **stb\_L** which is an inverted form of the **stb** *i.e.* an active low **stb** signal.

The three configuration registers holds 24 bits in total. The bit assignments of Configuration Register 0 are given in the Table 3.1. The bit assignments of Configuration Register 1 are provided in Table 3.2. Finally, the bit assignments for Configuration Register 2 are presented in Table 3.3. All three configuration registers are asynchronously reset when the master reset **reset** L signal goes low.

| Configuration | BIT       | Name             | Function                                                  |  |

|---------------|-----------|------------------|-----------------------------------------------------------|--|

| Register      | Poisition | TVanic           | runction                                                  |  |

| config_reg_0  | 0         | USE_EVEN_PULSER  | 0:Default                                                 |  |

| comig_reg_o   |           | OSELEVENT CESEIT | 1: Pulsing EVEN channels                                  |  |

| config_reg_0  | 1         | USE_ODD_PULSER   | 0: Default                                                |  |

| comig_reg_o   |           | OSE_ODD_I OESEI( | 1: Pulsing ODD channels                                   |  |

| config_reg_0  | 2         | NOWLIN_CAP0      |                                                           |  |

| config_reg_0  | 3         | NOWLIN_CAP1      | Selects one of the 16 capacitors  to set the NOWLIN delay |  |

| config_reg_0  | 4         | NOWLIN_CAP2      |                                                           |  |

| config_reg_0  | 5         | NOWLIN_CAP3      | (0.5pF to 8 pF)                                           |  |

|               | 6         | NOWLIN_MODE      | 1: Short Mode                                             |  |

| config_reg_0  |           |                  | (Rise time constant: 1ns - 16ns)                          |  |

|               |           |                  | 0: Long Mode                                              |  |

|               |           |                  | (Rise time constant: 12ns - 192ns)                        |  |

| config_reg_0  |           | DITEED DIVE HO   | 0: Bias is 50mv                                           |  |

|               | 7         | BUFFER_BIAS_HG   | 1: Bias is 20mv                                           |  |

Table 3.1: Bit assignments of configuration register 0

| Configuration  | BIT                           | Name                                        | Function                           |

|----------------|-------------------------------|---------------------------------------------|------------------------------------|

| Register       | Position                      |                                             |                                    |

| config_reg_1   | 0                             | BUFFER_BIAS_HG_POL                          | 0: Positive Polarity               |

|                |                               |                                             | 1: Negative Polarity               |

| config_reg_1   | config_reg_1 1 BUFFER_BIAS_LG |                                             | 0: Bias is 50mv                    |

|                |                               | _ 0 _ 1 0 _ 0 _ 0 _ 0 _ 0 _ 0 _ 0 _ 0 _ 0 _ | 1: Bias is 20mv                    |

| config_reg_1   | 2                             | BUFFER_BIAS_LG_POL                          | 0: Positive Polarity               |

| 0011118-1-08-1 | _                             |                                             | 1: Negative Polarity               |

| config_reg_1   | 3                             | AUTO_PEAK                                   | 0: Use take_event in peak detector |

|                |                               |                                             | 1: Use comparator output           |

| config_reg_1   | config_reg_1 4 SEL_SHAPER     |                                             | 0: Routes peak detector to output  |

| comig_reg_r    | <b>T</b>                      |                                             | 1: Routes shaper signal to output  |

| config_reg_1   | 5                             | AGND_TR0                                    | Allows to adjust ACND voltage      |

| config_reg_1   | 6                             | AGND_TR1                                    | Allows to adjust AGND voltage      |

| config_reg_1   | 7                             | AGND_TR2                                    | (1.4 to 1.8v in 50mV step)         |

Table 3.2: Bit assignments of configuration register 1

| Configuration<br>Register | BIT<br>Position | Name            | Function                                                                           |

|---------------------------|-----------------|-----------------|------------------------------------------------------------------------------------|

| config_reg_2              | 0               | TVC_2_USEC_MODE | 0: TVC 500 nsec range 1: TVC 2 usec full range                                     |

| config_reg_2              | 1               | EXT_CHARGE_AMP  | 0: Use internal charge amp 1: Use external charge amp                              |

| config_reg_2              | 2               | HOLES           | 0: Electrons Collection 1: Holes Collection                                        |

| config_reg_2              | 3               | DLY_VC0         | 41.4                                                                               |

| config_reg_2              | 4               | DLY_VC1         | 4 bit value that determines the                                                    |

| config_reg_2              | 5               | DLY_VC2         | 16 delay times by the auto reset block before the channels auto reset.             |

| config_reg_2              | 6               | DLY_VC3         | before the channels auto reset.                                                    |

| config_reg_2              | 7               | DLY_VC4         | 1 bit that determines the width of the digital reset to be either 100nsec or 1usec |

Table 3.3: Bit assignments of configuration register 2

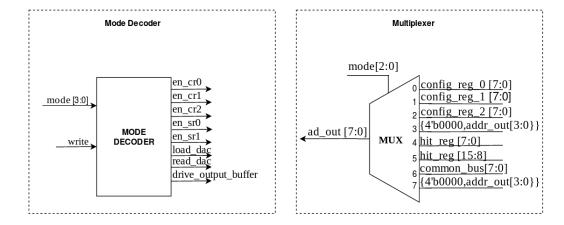

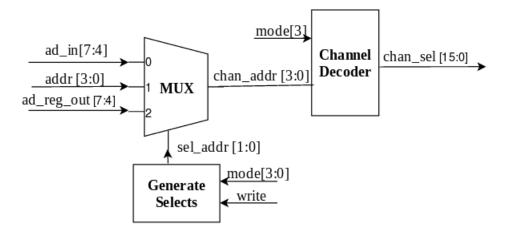

# 3.2.3 Mode Decoding Circuitry

On the rising edge of **stb**, the **write** signal selects whether data needs to be written into a register or read out of a register. Specifically, when the **write** signal is high then depending on the **mode**, the configuration data will be written into the appropriate configuration register, shadow register, or dac register in the designated channel. The data transfer occurs on the falling edge of the **stb**. If **write** is low then depending on the **mode**, the appropriate register will be read out of the chip.

Mode decoding circuitry is shown in Figure 3.3. It is composed of a mode decoder and a multiplexer block which implements combinational logic used to compare the write, mode and address bits with the encoded logic in them and performs the specified operation. Initially, the address and mode information present on the 8-bit wide ad\_in data bus is loaded into the address register on the rising edge of stb. Then these address and mode bits are compared with the hard-coded logic implemented in the mode decoder and multiplexer circuits.

Figure 3.3: Mode Decoding Logic implementation in common channel

Mode Decoder: The hard-coded values in the mode decoder are set to match the four mode bits and write signal on the chip that must select the specific register. In

addition it also matches the address of the channel the register is present then the specified register's enable signal is made active to write 8-bit configuration data into the designated register on the falling edge of the stb.

The en\_cr0 signal is an enable used to load data into Configuration Register 0. The en\_cr1 signal is an enable used to load data into Configuration Register 1. The en\_cr2 signal is an enable used to load data into Configuration Register 2. The load\_dac signal is an enable used to write configuration data into the DAC register in the channel pointed to by the address bits. The read\_dac signal is used to read the contents of the DAC register of the selected channel. The en\_sr0 is an enable used to load the lower 8 bits of the shadow register with data, whereas en\_sr1 is an enable used to load the upper 8 bits of the shadow register with data on the 8-bit ad\_in bus coming from the FPGA. The drive\_output\_buffer signal is sent to all the sixteen signal channels and is used to readout the selected channel.

Multiplexer: The Multiplexer is used to select one of the eight input lines. The lower three bits of **mode** is the control bus that is used to select which input should be connected to **ad\_out** which is an 8-bit output bus used to send digital data to the FPGA from the HINP5 chip. The various modes of operation are detailed in Table 3.4.

| write | mode [2:0] | Operation                        | Comments                                                                                                                                       |

|-------|------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | "000"      | ad_out < config_reg_0[7:0]       | Read out the contents of configuration register 0                                                                                              |

| 0     | "001"      | ad_out <— config_reg_1[7:0]      | Read out the contents of configuration register 1                                                                                              |

| 0     | "010"      | ad_out < config_reg_2[7:0]       | Read out the contents of configuration register 2                                                                                              |

| 0     | "011"      | ad_out < {4'b0000,addr_out[3:0]} | 4-bit encoded channel address is lower nibble and upper nibble is all zeros. In this mode channel address is derived from the shadow register. |

| 0     | "100"      | ad_out < hit_reg_lower[7:0]      | Read out the lower byte of the hit register                                                                                                    |

| 0     | "101"      | ad_out < hit_reg_upper[15:8]     | Read out the upper byte of the hit register                                                                                                    |

| 0     | "110"      | ad_out <— common_bus[7:0]        | Read out the contents in the common_bus                                                                                                        |

| 0     | "111"      | ad_out < {4'b0000,addr_out[3:0]} | 4-bit encoded channel address is lower nibble and upper nibble is all zeros. In this mode channel address is derived from the hit register     |

Table 3.4: Modes of Operation

| 1 | "000"     | $config\_reg\_0 < ad\_in[7:0]$ | Loads configuration                   |

|---|-----------|--------------------------------|---------------------------------------|

|   |           | -                              | register 0 (on posedge stb_L)         |

| 1 | "001"     | $config\_reg\_1 < ad\_in[7:0]$ | Loads configuration                   |

|   | 1 001     |                                | register 1 (on posedge stb_L)         |

| 1 | "010"     | $config\_reg\_2 < ad\_in[7:0]$ | Loads configuration                   |

|   | 1 010     |                                | register 2 (on posedge stb_L)         |

| 1 | 1 "011"   | addr_in <— ad_in[7:4]          | 4-bit channel address supplied        |

| 1 |           |                                | by the FPGA                           |

|   | 1 "100"   | shadow_reg_lower <— ad_in[7:0] | Loads lower byte of the shadow        |

| 1 |           |                                | register (on posedge stb_L) with      |

|   |           |                                | data from the FPGA                    |

|   | 1 "101"   | shadow_reg_upper <— ad_in[7:0] | Loads upper byte of the shadow        |

| 1 |           |                                | register (on posedge stb_L) with data |

|   |           |                                | from the FPGA                         |

|   |           |                                | Loads dac_register in channel         |

|   | 1 "110"   | dac_reg(addr) <— ad_in[7:0]    | pointed to by addr                    |

| 1 |           |                                | (i,e upper 4 bits of ad_reg).         |

|   |           |                                | Uses the load_dac signal and          |

|   |           |                                | the sel_chan[15:0] vector             |

| 1 | "111"     | 11" addr_in <— ad_in[7:4]      | 4-bit channel address supplied        |

| 1 | 1   "111" |                                | by the FPGA                           |

Table 3.5: Modes of Operation Continued

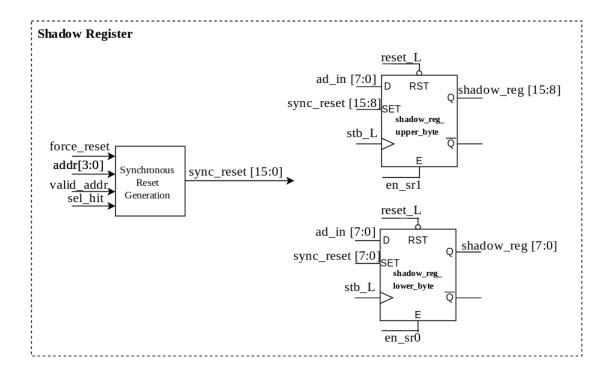

## 3.2.4 Shadow Register

The common channel contains a register which we call the Shadow Register (represented as shadow\_reg in Figure 3.2). Logic associated with this register is illustrated in Figure 3.4. The Shadow Register is 16-bits wide and has an enable and an asynchronous reset. The lower and upper bytes of the Shadow Register have different enable inputs but share a common asynchronous reset. In Figure 3.4, the en\_sr0 and en\_sr1 inputs are enables for the lower and upper bytes of the register, respectively. The signal reset\_L is a master reset signal that asynchronously resets the Shadow Register.

The enables for the shadow register are active when the shadow register mode is selected. If **en\_sr0** is active then the 8-bit data from FPGA present on the **ad\_in** bus is registered into the lower byte of the Shadow Register on the falling edge of the **stb\_L** and if **en\_sr1** is active then the 8-bit data from FPGA is registered into the upper byte of Shadow Register on the falling edge of the **stb**.

In addition to the asynchronous reset described above, individual bits in the register can be synchronously reset. The channel address (addr[3:0]) determines which bit will be reset. A valid\_addr bit, if set, indicates that the address generated is a valid address. If force\_reset which comes from the FPGA is asserted then the respective bit will be reset provided shadow register mode has been selected.

When radiation strikes a channel, a 1-bit **hit** register present in that channel is set. Then, if the **take\_event** signal comes along, the data in the channels that are hit are readout and and the hit register in that channel is reset. Generally, only channels whose hit register has been set are readout. However, there are applications where the physicists would like to alter which channels are readout. It is in these applications where the shadow register is useful. For example, one can read the hit register and

based on its contents decide which channels to read out and then write to the shadow register. The shadow register can then be used in the readout process.

Figure 3.4: Shadow Register

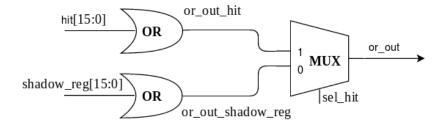

## 3.2.5 OR Generation

The **or\_out** signal indicates whether or not there are channels which still must be read out [Sadasivam, 2002]. See Figure 3.5. The hit-registers in the sixteen channels, **hit**[15:0], are logically OR'ed to produce the **or\_out\_hit** signal. The bits of the shadow register, **shadow\_reg**[15:0], are also logically OR'ed to produce **or\_out\_shadow\_reg**. If the control signal, **sel\_hit**, is high, the **or\_out\_hit** is selected for use as the **or\_out** signal else the **or\_out\_shadow\_reg** is used. The output from this circuit indicates that at least one channel has yet to be readout.

Figure 3.5: Circuit that generates OR\_OUT signal

## 3.2.6 Channel Address Generation Circuitry

The Channel Address Generation (CAG) circuit produces a 4-bit channel address. See Figure 3.6. Channels are encoded by a priority encoder. The lower channel number, the higher priority. The input to the priority encoder is either 16-bit hit register or the 16-bit shadow register. The sel\_hit determines which one. This sel\_hit control signal of 1-bit, selects one of the two inputs to the output line in the 2-1 multiplexer. Our logic includes a flag, valid\_addr, which indicates whether or not the channel address 0 is valid. The operation of the CAG module is summarized in Table 3.6.

Figure 3.6: Channel Address Generation Circuit

| INPUTS OUTPUTS      |           | ODED ATTION   |                                                                                |  |

|---------------------|-----------|---------------|--------------------------------------------------------------------------------|--|

| $encoder\_in[15:0]$ | addr[3:0] | $valid\_addr$ | OPERATION                                                                      |  |

| 0000_0000_0000_0000 | 0000      | 0             | The 4-bit binary address generated is not valid since no channel is being hit. |  |

| XXXX_XXXX_XXXX1     | 0000      | 1             |                                                                                |  |

| XXXX_XXXX_XXXX_XX10 | 0001      | 1             |                                                                                |  |

| XXXX_XXXX_XXXX_X100 | 0010      | 1             | The 4-bit binary address                                                       |  |

| XXXX_XXXX_XXXX_1000 | 0011      | 1             | of channel that is being hit                                                   |  |

| XXXX_XXXX_XXX1_0000 | 0100      | 1             | by radiation, generated by                                                     |  |

| XXXX_XXXX_XX10_0000 | 0101      | 1             | looking at the least significant                                               |  |

| XXXX_XXXX_X100_0000 | 0110      | 1             | bits of the encoder_in[15:0]                                                   |  |

| XXXX_XXXX_1000_0000 | 0111      | 1             | first then the most significant                                                |  |

| XXXX_XXX1_0000_0000 | 1000      | 1             | ones.Note: 1 represents that                                                   |  |

| XXXX_XX10_0000_0000 | 1001      | 1             | the channel is hit, 0                                                          |  |

| XXXX_X100_0000_0000 | 1010      | 1             | represents that the channel is                                                 |  |

| XXXX_1000_0000_0000 | 1011      | 1             | not hit & X notations                                                          |  |

| XXX1_0000_0000_0000 | 1100      | 1             | represents don't cares, X                                                      |  |

| XX10_0000_0000_0000 | 1101      | 1             | can be either hit or not hit.                                                  |  |

| X100_0000_0000_0000 | 1110      | 1             |                                                                                |  |

| 1000_0000_0000_0000 | 1111      | 1             |                                                                                |  |

Table 3.6: Truth Table of Priority Encoder

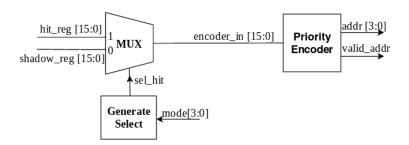

#### 3.2.7 Channel Select Generation Circuitry

The Channel Select Generation (CSG) circuit generates a 16-bit wide channel select bus, **chan\_sel**. Each bit of the **chan\_sel** bus goes into one of the 16 signal processing channels. For example, the **chan\_sel** bit of the specified channel must be active to write the data from the FPGA into the channel's DAC register. There are several different circuits within a channel which need the channel select.

There are three sources for the channel addresses used to generate the channel selects. These are ad\_in, addr, ad\_reg\_out. See Figure 3.7. The appropriate 4-bit channel address is selected depending on the mode and write signals. Then, based on the channel address, one of the 16 channel select lines will be active. However, if the most significant bit of the mode bus is active then all the channel select lines will be active.

Figure 3.7: Channel Select Generation Circuit

## 3.2.8 4-to-16 Decoder