# Development of a Pulse Shape Discrimination IC

Michael Hall

Southern Illinois University Edwardsville

VLSI Design Research Laboratory

October 20, 2006

### Design Team

### **Southern Illinois University Edwardsville:**

- Dr. George Engel (PI)

- Michael Hall (graduate student)

- Justin Proctor (graduate student)

### **Washington University in St. Louis:**

- Dr. Lee Sobotka (Co-PI)

- Jon Elson (electronics specialist)

- Dr. Robert Charity

### Western Michigan:

Dr. Mike Famiano (Co-PI)

## NSF Proposal (Funded)

- Design, simulate, and fabricate a PSD chip suitable for use with

- CsI(TI) (used for charge-particle discrimination)

- Liquid Scintillator (used for neutron-gamma discrimination), for example:

- Nuclear Enterprises (NE213)

- ■Bicron (BC501A)

- 8 channel "prototype" chip

- 16 channel "production" chip

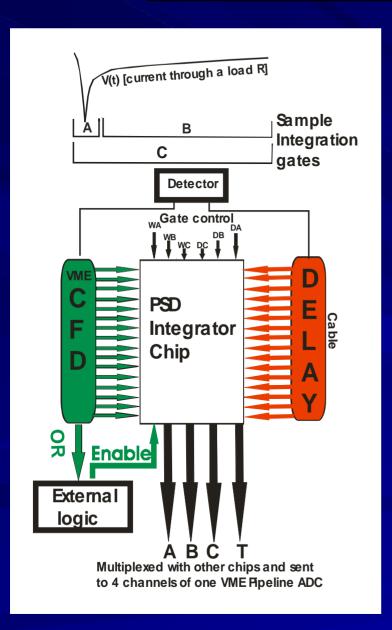

## Overview of PSD System

- Detector (PMT or photodiode)

- External discriminators (CFDs)

- External delay lines so we can start integrations before arrival of pulse

- External control voltages determine Delay and Width of integration periods

- Outputs A, B, C integrator voltages and relative time, T

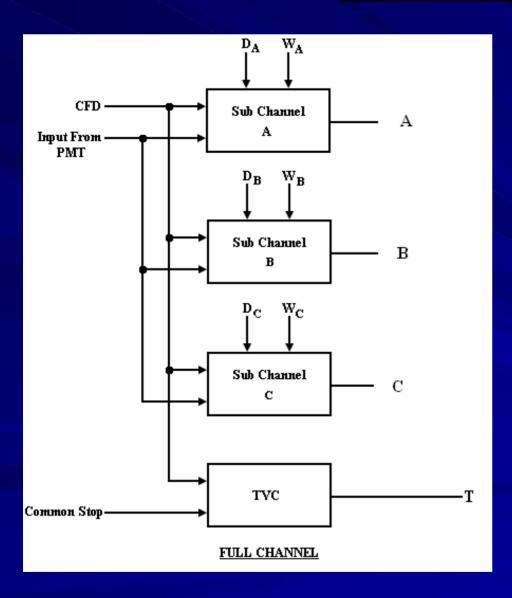

## **Channel**

- 3 on-chip subchannels for integrators A, B, C

- Delay and width of integrators set by externally supplied control voltages

- Timing relative to a common stop signal

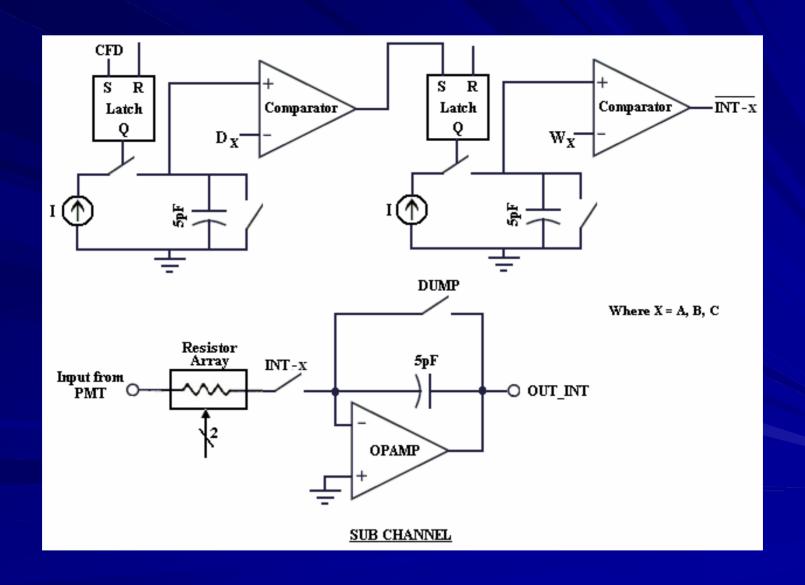

## Sub-Channel

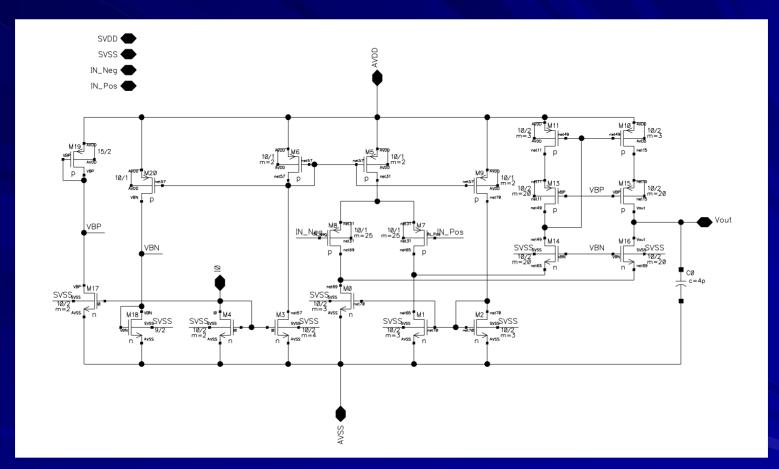

## Op Amp to be Used in Integrator

Gain Bandwidth Product: 34 MHz

Low-frequency open-loop gain: 74 dB

Supply Current: 1.25 mA Power Consumption: 6 mW

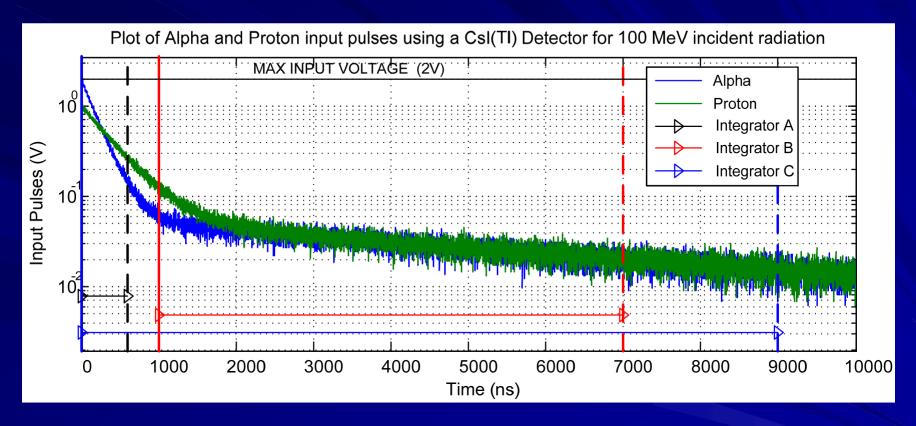

### Simulated Input Pulse for CsI(TI) Detector

- Integrators

- A 0 to 600 ns

- B 1000 to 7000 ns

- C 0 to 9000 ns

- Integration periods at the beginning of the signal are assumed to start before the pulse (at -5 ns).

## Noise Sources

- **Poisson** noise due to random arrival of discrete electrons

- Electronics Noise

- <u>Jitter</u> noise created by an uncertainty in the integration start time and in the width of integration period

- <u>RI</u> thermal noise from the integrating resistor sampled onto the integrating capacitor

- OTA thermal noise of the op amp sampled onto the integrating capacitor

- OTA (+) continuous additive input-referred thermal noise of the op amp

- 1/f 1/f noise of the op amp sampled onto the integrating capacitor

- 1/f (+) continuous additive input-referred 1/f noise of the op amp

- ADC quantization noise of a 12-bit converter

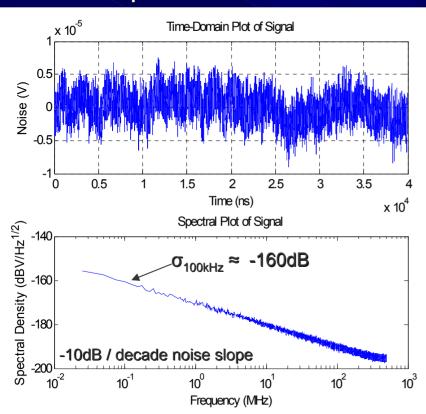

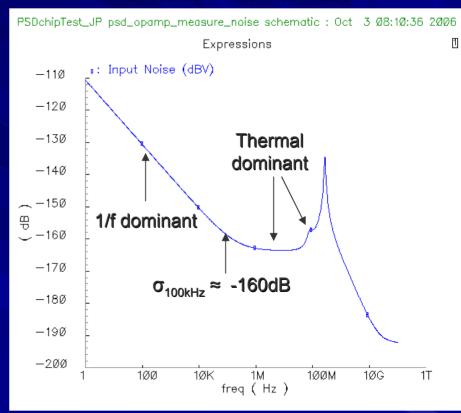

### 1/f Noise Model

#### **Input Referred 1/f Noise**

#### 1/f Noise + Thermal Noise

MATLAB Equivalent Model of 1/f Noise K = 8.745e-12 (constant for 1/f model)

Spectre Simulation of OTA Noise

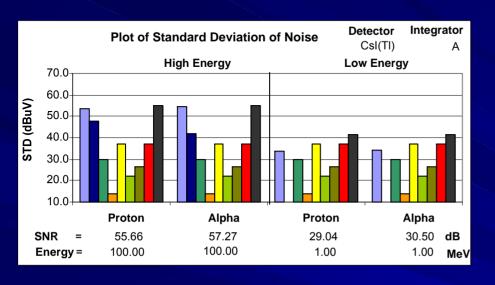

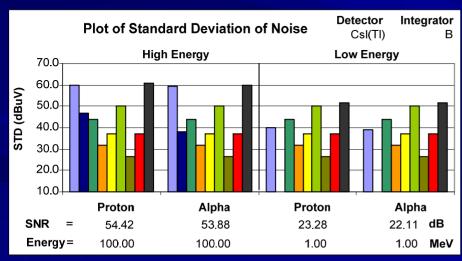

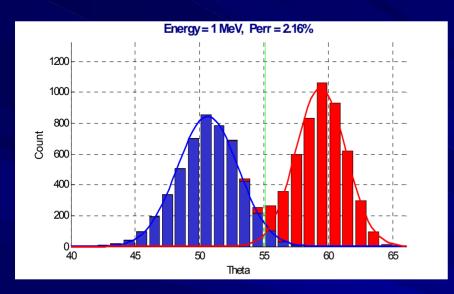

## Relative Importance of Noise Sources on Performance for CsI(TI) Detector

- Detector: Csl(Tl)

- Integrators

- A 0 to 600 ns, RI = 100kΩ

- B 1000 to 7000 ns, RI = 40kΩ

- C 0 to 9000 ns, RI = 100kΩ

- CI = 10pF

- Jitter

- Start: 1.00 nsPeriod: 0.50 ns

- ADC: 12 bit

- Jitter

- RI

- OTA

- □ OTA (+)

- 1/f

- 1/f (+)

- ADC

- Total

### Summary of Noise Analysis (CsI)

- Poisson noise dominates for high-energy particles, but tends to be on par with electronics noise (10 pf integrating capacitor) for low-energy particles.

- Jitter induced noise is not a dominant noise source, but is on par with Poisson noise for the A integrator at high energy.

- 1/f noise dominates for low-energy particles on the B and C integrators

- Electronics noise on par with quantization noise of 12-bit ADC except for 1/f noise for B and C integrators at low energy.

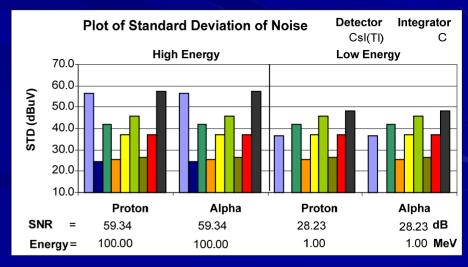

### Pulse Shape Discrimination Plot for CsI(TI) Detector

- Detector: CsI(TI)

- Integrators:

A, B

- Energy Max:100 MeV (for 2V at input of integrator)

- Energy Range:1 100 MeV

- Includes all noise sources

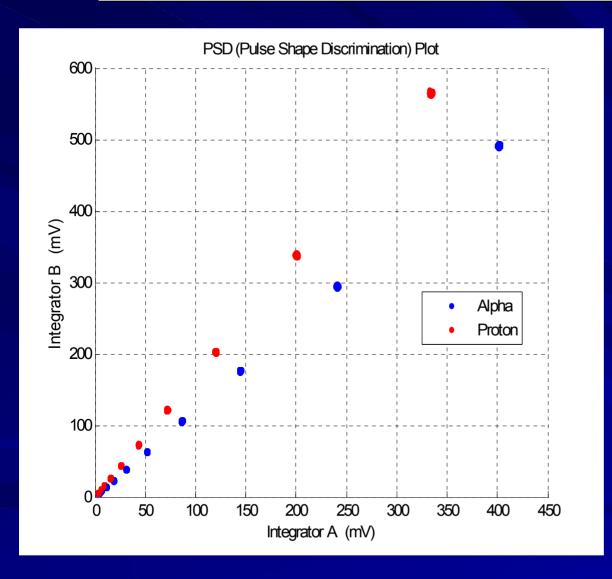

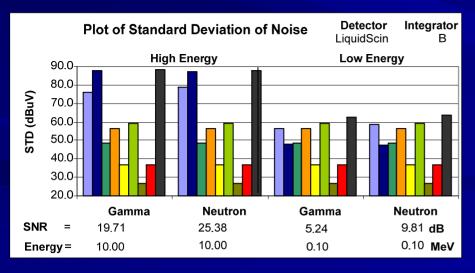

## Angular PSD Plots (Csl)

- Detector: Csl(Tl)

- Integrators:

A, B

- Energy Max: 100 MeV

- Energy Range: 1 – 100 MeV

- 5000 realizations

- Includes all noise sources

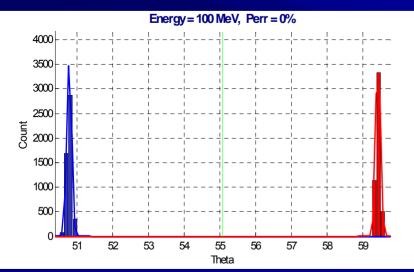

### Simulated Input Pulse for Liquid Scintillator Detector

- Integrators

- A 0 to 200 ns

- B 30 to 202 ns

- C 50 to 204 ns

- Integration periods at the beginning of the signal are assumed to start before the pulse (at -5 ns) (no jitter at the start of integration).

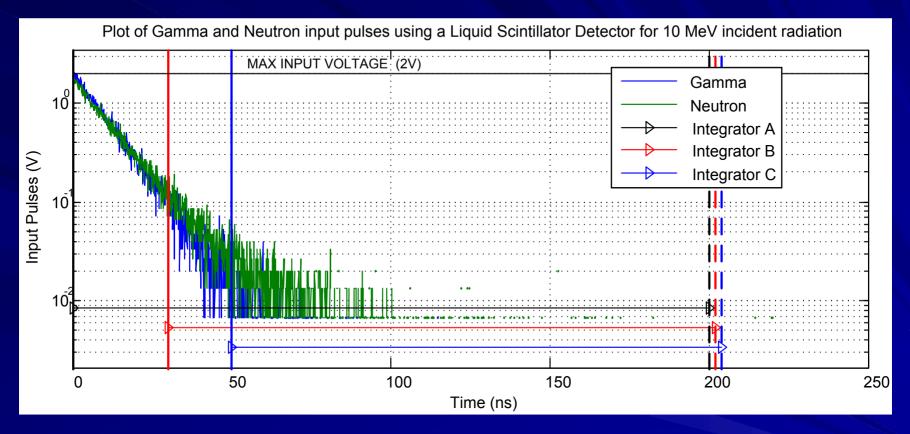

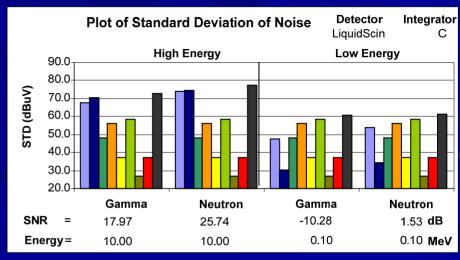

## Relative Importance of Noise Sources on Performance for Liquid Scintillator Detector

- Detector: Liquid Scintillator

- Integrators

- A 0 to 200 ns, RI =  $2k\Omega$

- B 30 to 202 ns, RI = 400Ω

- C 50 to 204 ns, RI = 400Ω

- CI = 10pF

- Jitter

- Start: 1.00 nsPeriod: 0.50 ns

- ADC: 12 bit

- Jitter

- RI

- OTA

- □ OTA (+)

- 1/f

- 1/f (+)

- ADC

- Total

# Summary of Noise Analysis (Liquid Scintillator)

- Poisson noise no longer dominates except for integrator A in which the integration begins before the start of the pulse.

- Jitter becomes *very* important for B and C integrators and dominates at high energy levels.

- Electronics noise (especially for B and C integrators) is significantly larger than the quantization noise of a 12-bit ADC but still on par with the Poisson noise.

- 1/f noise is on par with the thermal noise for low-energy particles on the B and C integrators.

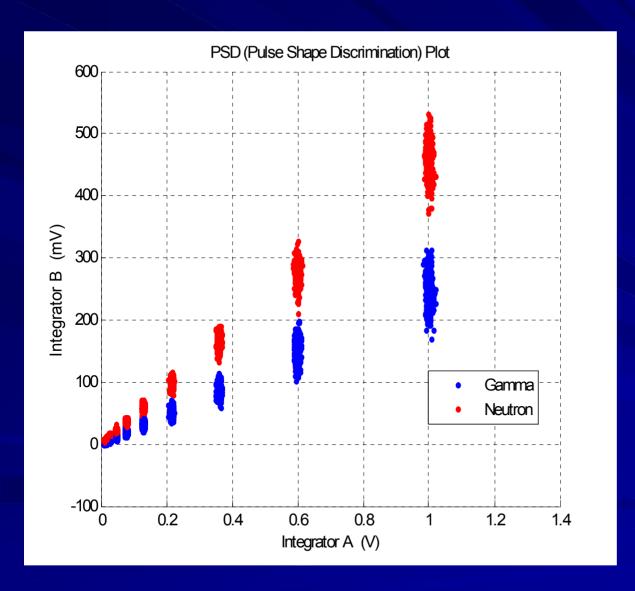

### Pulse Shape Discrimination Plot for Liquid Scintillator Detector

- Detector: LiquidScintillator

- Integrators: A, B

- Energy Max:10 MeV (for 2V at input of integrator)

- Energy Range:0.1 10 MeV

- Includes all noise sources

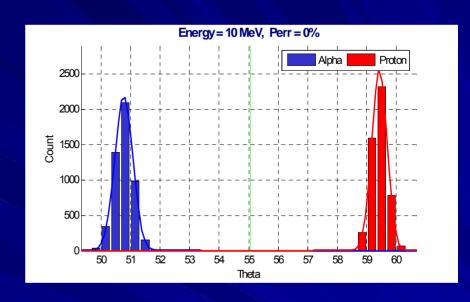

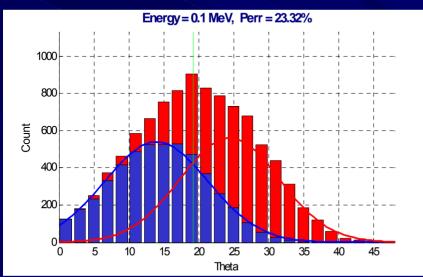

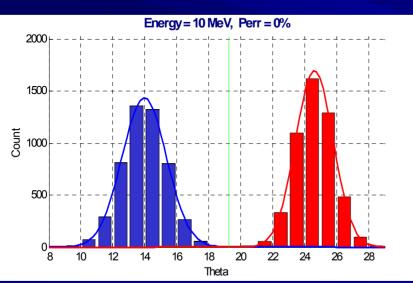

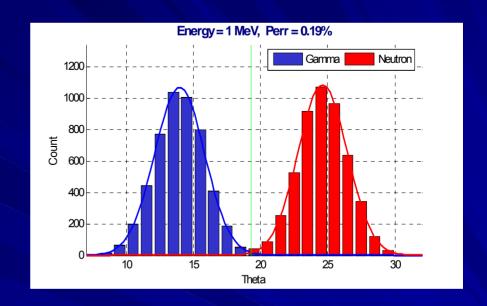

### Angular PSD Plots (Liquid Scintillator)

- Detector: Liquid Scintillator

- Integrators: A, B

- Energy Max:10 MeV

- Energy Range: 0.1 – 10 MeV

- 5000 realizations

- Includes all noise sources

# Analytical Predictions of Variance of Angular PSD Plots

$$\operatorname{var}(\theta) = \frac{\sin^2 2\theta}{4} \cdot \left[ \frac{1}{SNR_A^2} + \frac{1}{SNR_B^2} \right]$$

$$FOM = \frac{\left|\theta_1 - \theta_0\right|}{\sqrt{\operatorname{var}(\theta_1) + \operatorname{var}(\theta_0)}}$$

- Variance of angular PSD plot depends on the signal-to-noise ratio of the A and B integrators.

- Small signal-to-noise ratios, which correspond to low-energy particles, results in a larger variance in angle which is consistent with simulation.

- Figure of merit (FOM) is computed as the difference between the means divided by the square root of the sum of the variances.

### Conclusions

- Proposed PSD IC will work very well with CSI detectors with performance limited by Poisson noise. Particles differing in energy by 40 dB can be easily discriminated.

- Proposed PSD IC will work reasonably well with Liquid Scintillator detectors with performance limited most likely by the level of timing jitter. Particles differing in energy by more than 20 dB will have high probability of misclassification.

- While the electronics noise dominates for the B and C integrators for both detectors at low energy, it is clearly worse for the Liquid Scintillator detector where it is significantly higher than the quantization noise of a 12-bit ADC.

### Conclusions

- Correlated double sampling to deal with 1/f noise does not appear mandatory.

- Poisson noise dominates in the A integrator for both CsI(TI) and Liquid Scintillator detectors at all energies except for the CsI(TI) at low energies.

- A 10 pF integrating capacitor will be used along with a bank of 8 resistors: 400 Ω, 1 kΩ, 2 kΩ, 4 kΩ, 10 kΩ, 20 kΩ, 40 kΩ, 100 kΩ

- The integrating op amp will consume 6 mW of power so for an 8 channel IC, the integrating op amps will require approximately 150 mW of power (300 mW for a 16channel IC).

### **Future Work**

- For a stochastic processes course, will create an optimizer to maximize the FOM on the PSD plots.

- Behavioral simulations to determine performance of on-chip time-to-voltage converters. Special attention will be given to reducing on-chip induced timing jitter.

- Behavioral level simulations (VerilogA) to verify functionality of one complete channel including read-out electronics

### **Future Work**

- Circuit design and simulation

- Layout

- Fabrication

- Testing of the IC