# Design of On-chip ADC for Custom ASICS Used in the Detection of Ionizing Radiation

by Dinesh Kumar Dasari, Bachelor of Science

A Thesis Submitted in Partial Fulfillment of the Requirements for the Master of Science Degree

Department of Electrical and Computer Engineering in the Graduate School Southern Illinois University Edwardsville Edwardsville, Illinois

August 2008

#### **ABSTRACT**

# DESIGN OF ON-CHIP ADC FOR CUSTOM ASICS USED IN THE DETECTION OF IONIZING RADIATION

by

#### Dinesh Kumar Dasari

Advisor: Dr. George L Engel

This thesis presents the design and simulation of a 12-bit, 2 MSample/sec Analog-to-Digital Converter (ADC). The ADC is intended for use in a family of integrated circuits (ICs) used in the detection of ionizing radiation. The ICs are being developed by the Integrated Circuit Design Research Laboratory at Southern Illinois University Edwardsville (SIUE). The current chip designs provide analog outputs. Storing data in a digital format on-chip before transmittal to a host computer over an "I2C-like" interface will result in improved system performance.

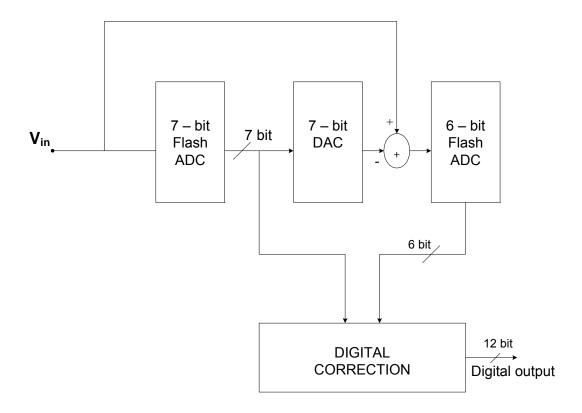

The ADC will be implemented in the future in a 5-Volt AMIS 0.5 µm, double-poly, tri-metal CMOS process (C5N). The converter described in this thesis employs a two-step flash technique with digital error correction. It is configured as a fully-differential circuit. The converter performs a 7-bit "coarse" flash conversion followed by 6-bit "fine" flash conversion, the results of which are then combined through a digital correction algorithm to produce the desired 12-bit output.

Electrical simulations demonstrate that the noise characteristics of the converter are consistent with those of a 12-bit quantizer. Simulations indicate that, in the presence of typical offset and mismatch errors, the effective number of bits (ENOB) will be 11.8. This work was initiated by the heavy-ion nuclear chemistry and physics group at Washington University in Saint Louis and is funded by NSF Grant #06118996.

ii

#### **ACKNOWLEDGEMENTS**

I would like to thank my mentor Dr. George Engel for his constant support, encouragement, and guidance throughout this project. I would also like to thank my fellow researchers: Harakrishna Valluru, Nagachaitanya Yelchuri, Hu Wang, and Nam Nguyen.

I would also like to thank Dr. Brad Noble and other ECE faculty members at SIUE who taught me many things that helped me with this project. I would also thank Mr. Steve Muren who was instrumental in providing the necessary equipment for the lab. I would also like to thank Arokia Nirmal for his help in the preparation of many of the drawings included in this thesis. Finally, I would like to extend my appreciation to my parents, my brother, cousins and friends whom have supported me all my life.

# TABLE OF CONTENTS

| ABSTRAC'  | Γ                                                                                                                                                                                                                                                                                                                       | ii                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ACKNOWL   | EDGEMENTS                                                                                                                                                                                                                                                                                                               | iii                                          |

| LIST OF F | IGURES                                                                                                                                                                                                                                                                                                                  | vi                                           |

| LIST OF T | ABLES                                                                                                                                                                                                                                                                                                                   | viii                                         |

| Chapter   |                                                                                                                                                                                                                                                                                                                         |                                              |

| 1.        | INTRODUCTION                                                                                                                                                                                                                                                                                                            | 1                                            |

|           | Background Integrated Circuits for Use in Nuclear Physics Need for On-Chip ADC Object and Scope of Thesis                                                                                                                                                                                                               | 3<br>11                                      |

| 2.        | ADC ARCHITECTURE                                                                                                                                                                                                                                                                                                        |                                              |

|           | Comparison of ADC Architectures Two-Step Flash Converter. Two-Step Algorithm First Stage Second Stage System Timing Digital Encoding Redundancy and Digital Correction Algorithm.                                                                                                                                       | 17<br>20<br>21<br>23                         |

| 3.        | Single-Ended to Differential Converter. Core operational amplifier. Reference Generator. First Stage Ladder. First Stage Comparator. Digital-to-Analog Converter. Residue Generator. Second Stage Ladder and Ladder Correction Circuit Second Stage Comparator Thermometer-to-Binary Encoder. Digital Correction Logic. | 32<br>34<br>36<br>37<br>40<br>45<br>51<br>54 |

| 4.        | SIMULATED PERFORMANCE OF ADC                                                                                                                                                                                                                                                                                            | 63<br>65                                     |

| 5. | SUMMARY/FUTURE WORK              | 74       |

|----|----------------------------------|----------|

|    | SummaryFuture Work               |          |

|    | REFERENCES                       | 77       |

|    | APPENDICES                       |          |

|    | A. VerilogA CodeB. MathCAD® Code | 81<br>85 |

# LIST OF FIGURES

| Figure |                                                                  | Page |

|--------|------------------------------------------------------------------|------|

| 1.1    | HINP16C based system                                             | 4    |

| 1.2    | Block diagram of HINP16C chip                                    | 5    |

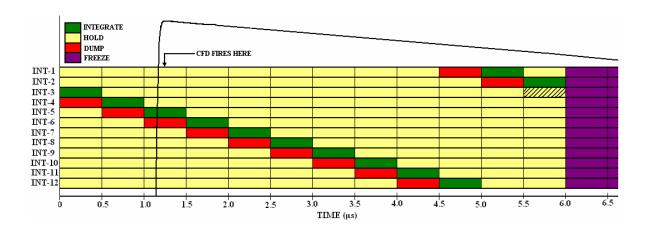

| 1.3    | Overview of analog pulse-shape discrimination integration scheme | 6    |

| 1.4    | Sample current pulses from CsI(Tl)                               | 7    |

| 1.5    | PSD plots demonstrating particle identification                  | 8    |

| 1.6    | AA-DSP logic                                                     | 10   |

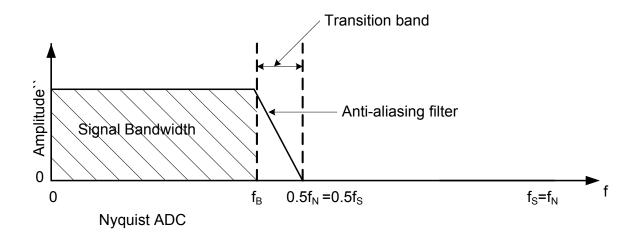

| 2.1    | Frequency spectrum of Nyquist-rate ADC and over-sampling ADC     | 15   |

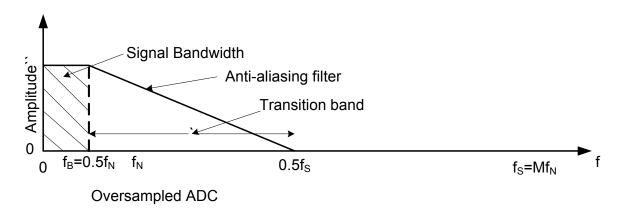

| 2.2    | ADC converter architecture                                       | 19   |

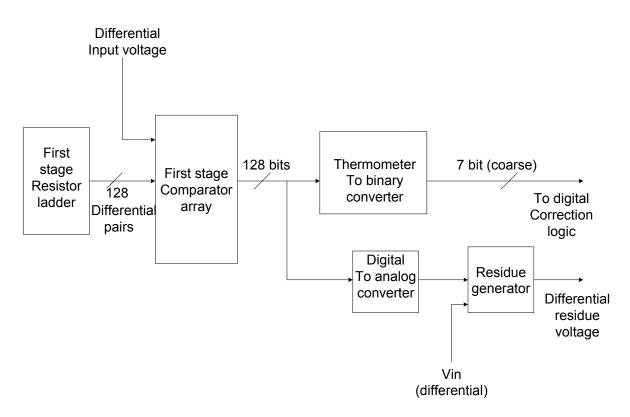

| 2.3    | Block diagram of first-stage electronics                         | 20   |

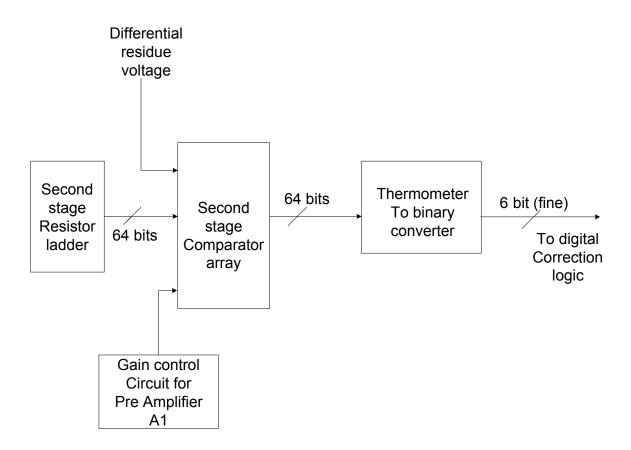

| 2.4    | Block diagram of second-stage electronics                        | 22   |

| 2.5    | System timing diagram                                            | 25   |

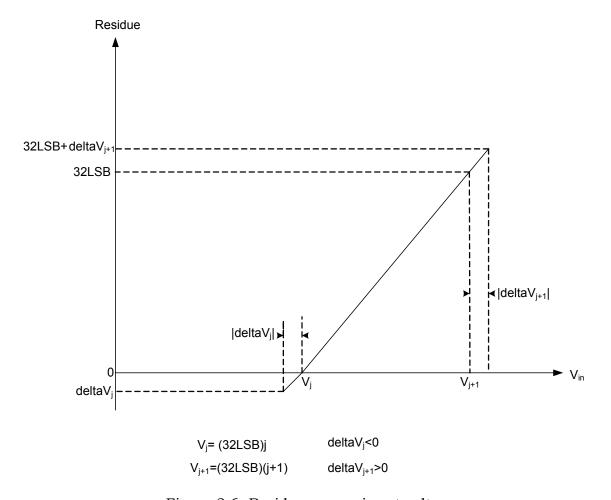

| 2.6    | Residue versus input voltage                                     | 28   |

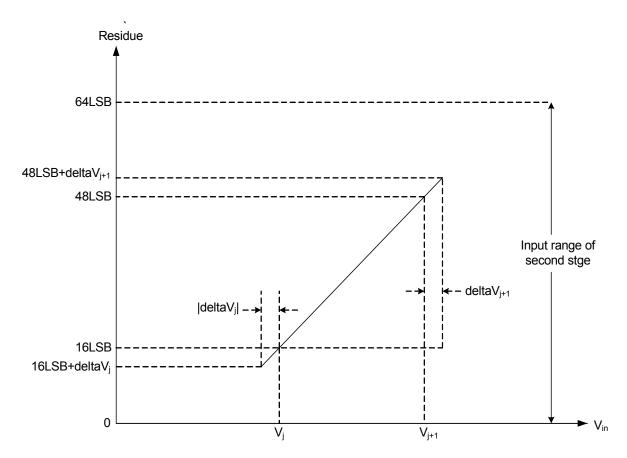

| 2.7    | Range expansion in A/D converter                                 | 29   |

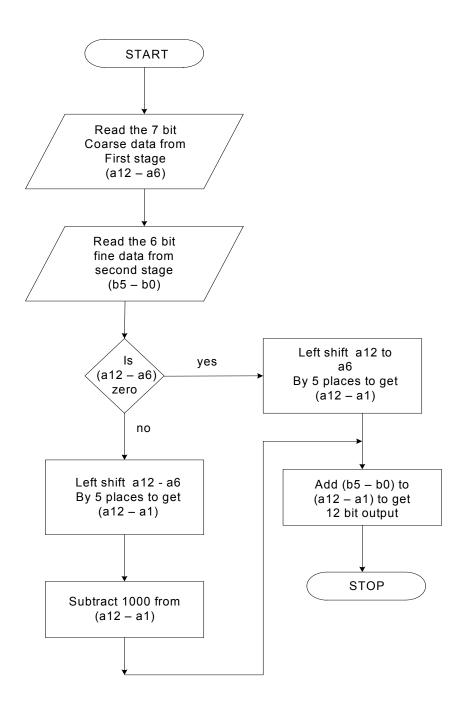

| 2.8    | Digital correction algorithm flowchart                           | 30   |

| 3.1    | Single-ended-to-differential conversion circuit                  | 33   |

| 3.2    | Reference generator circuit                                      | 35   |

| 3.3    | First-stage ladder circuit                                       | 37   |

| 3.4    | First-stage comparator block diagram                             | 39   |

| 3.5    | First-stage comparator schematic                                 | 40   |

| 3.6    | DAC unit cell                                                    | 42   |

| 3.7    | DAC_plus and DAC_minus outputs of a ramp input                   | 43   |

| 3.8    | DAC transfer characteristic                                      | 44   |

| 3.9    | Differential DAC error plot                                      | 44   |

| 3.10   | Residue generator circuit                                        | 46   |

| 3.11 | OTA schematic                                          | . 47 |

|------|--------------------------------------------------------|------|

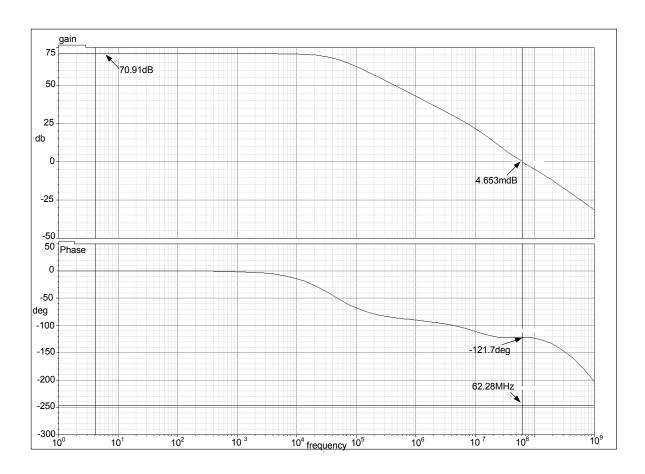

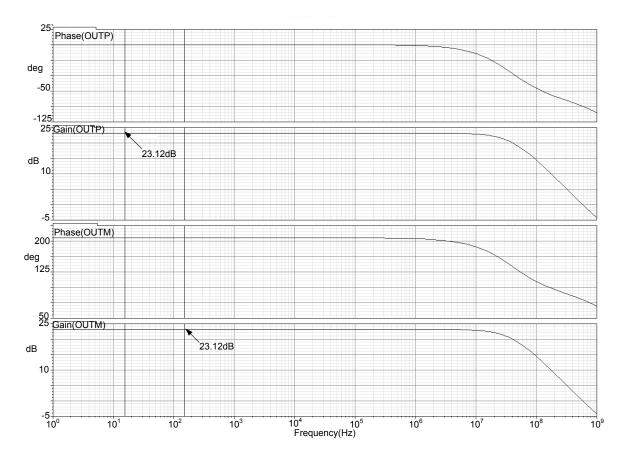

| 3.12 | OTA frequency response                                 | . 48 |

| 3.13 | Residue generator output                               | 50   |

| 3.14 | Settling behavior of residue generator                 | 51   |

| 3.15 | Second-stage ladder                                    | . 52 |

| 3.16 | Ladder correction circuit                              | . 53 |

| 3.17 | Second-stage comparator block diagram                  | . 55 |

| 3.18 | Preamplifier A1schematic                               | 56   |

| 3.19 | Gain control circuit for preamplifier A1               | . 57 |

| 3.20 | Bode plot for preamplifier A1                          | . 58 |

| 3.21 | Thermometer-to-binary encoder logic                    | 60   |

| 3.22 | Digital correction logic                               | 62   |

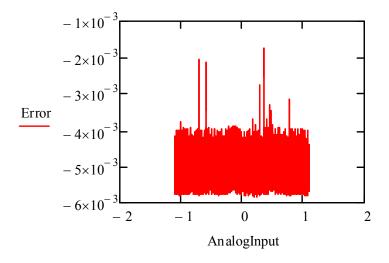

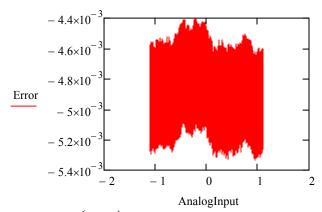

| 4.1  | Error plot of ideal 12 bit ADC                         | 64   |

| 4.2  | ENOB versus percentage of mismatch in resistors.       | 65   |

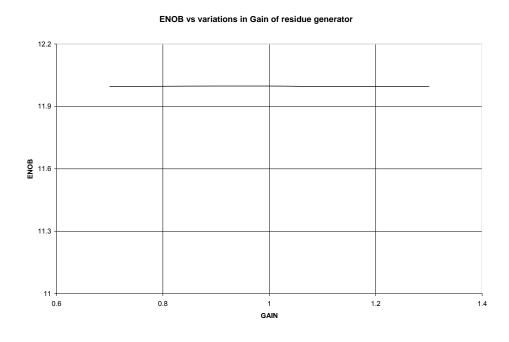

| 4.3  | ENOB versus variation in Gain of residue generator     | 66   |

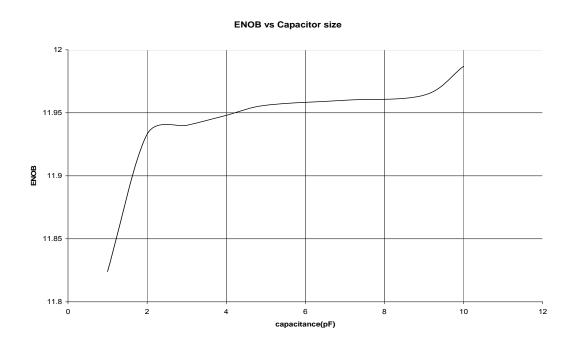

| 4.4  | ENOB versus mismatch in capacitors                     | 67   |

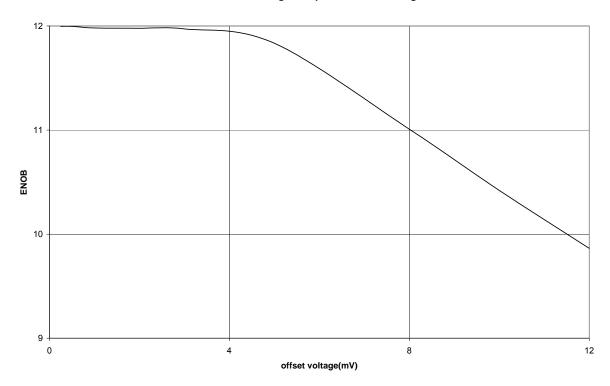

| 4.5  | ENOB versus first-stage comparator offset voltages     | 68   |

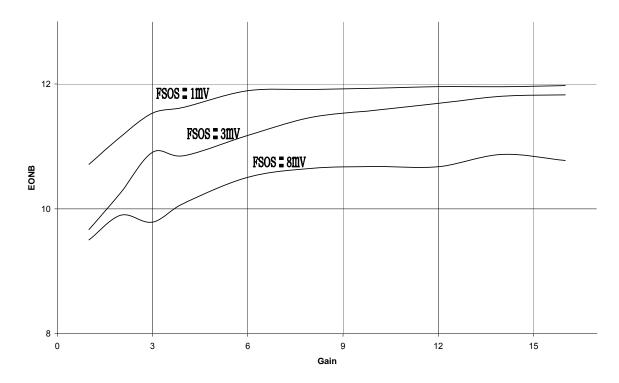

| 4.6  | ENOB versus gain of preamplifier A1                    | 69   |

| 4.7  | Error plot of the ADC with a first stage offset of 8mV | 70   |

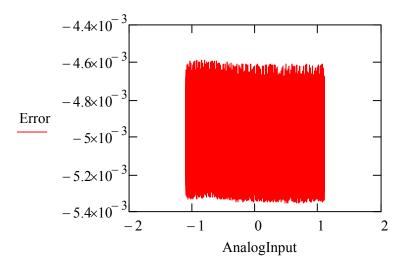

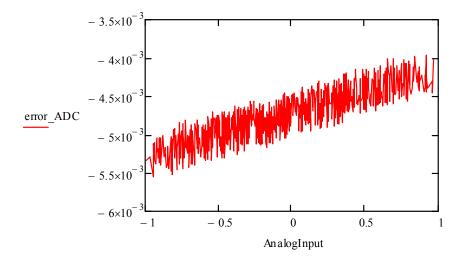

| 4.8  | Error plot of the ADC simulated using Spectre®         | 71   |

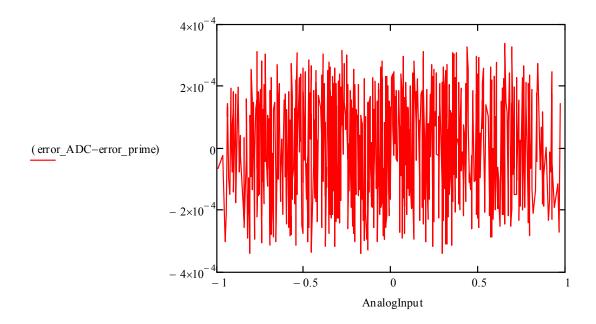

| 4.9  | Error plot of Figure 4.8 with systematic error removed | . 72 |

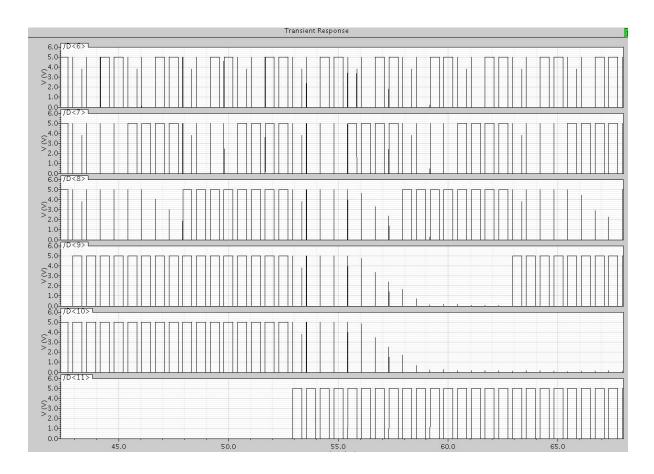

| 4.10 | ADC response to ramp input                             | . 73 |

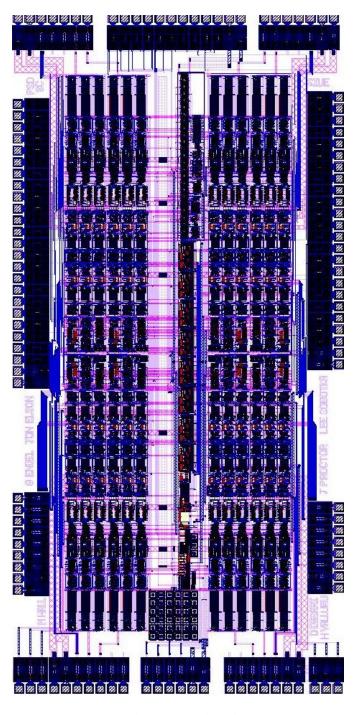

| 5.1  | PSD chip layout                                        | 76   |

# LIST OF TABLES

| Table |                                                           | Page |

|-------|-----------------------------------------------------------|------|

| 2.1   | Classification of ADC architectures                       | 15   |

| 3.1   | Transistor sizes for first-stage comparator schematic     | 39   |

| 3.2   | Gain and phase margin of OTA for multiple process corners | 48   |

| 3.3   | Transistor sizes for OTA schematic                        | 49   |

| 3.4   | Transistor sizes for ladder correction circuit            | 54   |

| 3.5   | Transistor sizes for preamplifier A1                      | 56   |

| 3.6   | Gain of preamplifier A1 as function of process corner     | 59   |

#### CHAPTER 1

#### INTRODUCTION

### **Background**

The IC Design Research Laboratory at Southern Illinois University Edwardsville (SIUE) is part of an interuniversity collaboration which has as its long-term goal the development of a family of multi-channel custom integrated circuits (ICs) suitable for use in a wide variety of low- and intermediate-energy nuclear physics experiments where the detection of ionizing radiation is needed. The greater collaboration includes researchers at Washington University in Saint Louis, Michigan State University, Western Michigan University, and Indiana University.

Often in nuclear physics experiments the type of radiation must be classified, the energy of the incident must be determined, and the position of interaction within the detector itself must be estimated [Sob:07]. The ICs which have already been designed and fabricated, as well as those currently under development contain the analog electronics that make the accomplishment of these scientific objectives possible. Moreover, someday these micro-chips may be used by the Department of Homeland Security (DHS) in nuclear threat detection systems deployed throughout the country.

The reasons why the collaboration became interested in developing a family of micro-chips for use in nuclear physics experiments include: (1) the need for high density signal processing in low- and intermediate-energy nuclear physics community is widespread,(2) no commercial chip was identified that was capable of doing what the researchers wanted, and (3) the scientists deemed it necessary for the "experimenter" to be in the "designer's seat".

Preliminary work on the ICs began in the year 2000 [Gan:00] [Mal:01]. Initially the development was funded through support from the nuclear reactions group in the Department of Chemistry at Washington University in Saint Louis; however, because of the success of the project over the years, the current work is funded by the National Science Foundation (NSF Grant #06118996).

While the initial intent was to use the ICs in nuclear physics experiments, we are now proposing to create a mini-center that will work on different aspects of nuclear threat detection systems for DHS. One aspect of our most recent proposal to NSF concerns the development of a suite of analog ASICs (Application Specific Integrated Circuits) for use with scintillation (Sc) and semiconductor solid-state (SS) detectors. Standard signal processing components would be developed in addition to novel elements including single, few, and "round-robin" charge integrators, chip-level filtering, and on-chip digitization (the topic of this thesis).

The goal of our group is to achieve a great simplification in digital-signal processing (DSP) by doing as much as possible in the front-end CMOS (Complementary Metal-Oxide Semiconductor) ASIC. Compact low-power CMOS digitizers are relatively slow. A full-blown DSP-based approach would require a digitizer with 14-bit resolution and a sample rate in excess of 100 MSamples/sec. Our group plans to overcome this limitation by using one of two analog schemes (one each for Sc and SS detectors) to reduce the time dependence of the signal to a few analog voltages that can be stored and subsequently digitized on-chip. We refer to the economical (low power, size, and money) strategy as Analog-Assisted Digital Signal Processing (AA-DSP).

It is the on-chip digitization of these analog output signals (from the various ICs under development) which is the topic of this Master's Thesis. In the following section, we briefly discuss in more detail the integrated circuits that we *have*

developed, *are* developing, and *will* develop over the next few years. In the subsequent section, we will enumerate the advantages of digitizing the analog signals on-chip as opposed to bringing the analog signals off-chip for digitization.

# **Integrated Circuits for Use in Nuclear Physics**

A significant focus of the proposed mini-center will be on the design of low-noise, high-performance analog integrated circuits for use with detectors for ionizing radiation. This work will build on our past and ongoing efforts. The principal example of the former is our HINP16C chip [Eng:07a, Sad:02]. An example of the latter is our current project to develop a Pulse-Shape Discrimination (PSD) chip [Eng:07b, Hal:07, Pro:07]. The PSD project will be extended in the future to a full Analog-Assisted DSP scheme (AA-DSP) with information compaction, as well as the digitization, done on the front-end chip. The former is necessary as the digitizers will be relatively slow (a few Msamples/sec). As we shall see in this thesis even the design of a 12-bit, 2 MSample/sec ADC in a 0.5 micron CMOS technology is quite challenging.

Our collaboration has successfully developed and implemented the HINP16C chip, now in wide use in basic nuclear science. In addition to our own group, groups at the National Superconducting Cyclotron laboratory (NSCL), Oak ridge National Laboratory (ORNL), Indiana University, and Western Michigan University use this chip. Nuclear Physics (NP) groups at Florida State and Louisiana State are building entire programs around this chip as well.

This CMOS ASIC, based on prior work by Spieler and Britton [Spi:05, Sim:95], is described in detail in [Eng:07a, Sad:02] and its integration into a large-scale system is presented in [Wal:07]. A sampling of the science (from our group) using this chip, can be found in [Cha:07b,Cha:07c]. A motherboard which is

capable of housing 16 chipboards (CBs) is shown in Figure 1.1. A representative CB supporting two HINP16C chips is present in the foreground. A single motherboard is capable of supporting 512 independent channels.

Figure 1.1: HINP16C based system

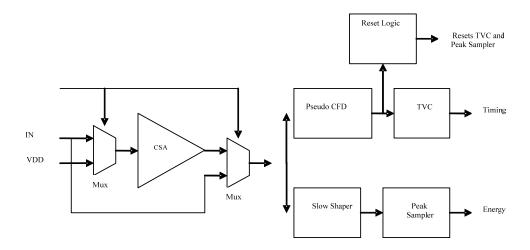

Each of the sixteen channels of HINP16C contains a charge sensitive amplifier (CSA) with two gain ranges, shaper, constant-fraction discriminator (CFD), peak detector, time-to-voltage converter (TVC), and analog output sequencing logic. On the other hand, this chip has **no** pulse-shape analysis capability and **relies on an external ADC** (Analog-to-Digital Converter) for digitization. A block diagram for a single channel of the HINP16C chip is illustrated in Figure 1.2.

Figure 1.2: Block diagram of HINP16C chip

The "Timing" and "Energy" outputs in Figure 1.2 are analog pulse trains which are currently digitized by an off-chip ADC. The ADC described in this thesis could be integrated into a future generation HINP16C chip. An ADC integrated with HINP16C is desirable for many reasons as we will discuss in the following section of this thesis.

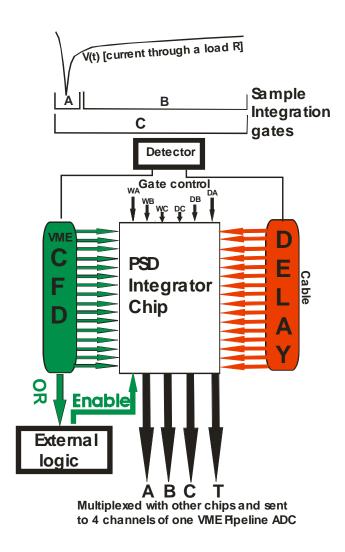

Signal-shape analysis capability (not possible with the HINP16C chip) is desirable in order to distinguish  $\gamma$ -rays, n's,  $\alpha$ -particles from cosmic or other background events from scintillator-based systems. The shape analysis is also needed for tracking applications in large volume Ge or any size CZT detector arrays. A now nearly completed NSF-funded project (chip has been fabricated but as yet to be tested and fully characterized) moved us into the PSD (Pulse Shape Discrimination) realm for scintillators. An eight-channel chip we call PSD8C, fully described in [Hal:07] and [Pro:07], utilizes CMOS technology to provide: a) integration of several regions of the analog signal, b) time-to-amplitude conversion, and c) generates pulse streams from each of the above for an *off-chip* ADC.

To focus our attention, we consider a PSD capable scintillator (e.g., CsI(Tl),  $LaCl_3$ :Ce [Hoe:05], stilbene, or BC501) and the analog electronics [Pro:07] illustrated in Figure 1.3.

Figure 1.3: Overview of analog pulse-shape discrimination integration scheme

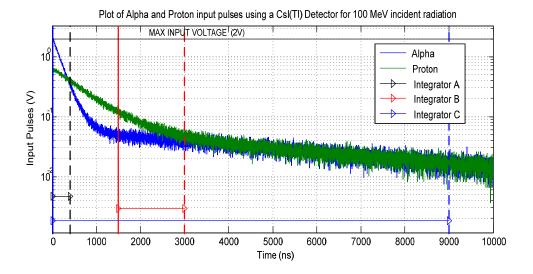

The photomultiplier tube generated current pulses are split to be used in logic and linear branches. Representative pulses [Hal:07] are depicted in Figure 1.4.

Figure 1.4: Sample current pulses from CsI(Tl) (alpha-blue and proton-green).

Timing signals are generated by compact, low-power constant-fraction discriminators recently developed by our collaboration. The individual logical timing signals and delayed linear signals are sent to the CMOS chip for multiple time region integration. The individual CFD logic signals ANDed with a global enable signal provide channel enables for three different integrations ( $\bf A$ ,  $\bf B$  &  $\bf C$ ). These integrations are performed with start times referenced to the individual discriminators. In addition, the amplitude,  $\bf T$ , produced is proportional to the difference in time between the individual discriminator firing and an external common stop reference. The delays in the integrators' starting times ( $\bf D_A$ ,  $\bf D_B$ ,  $\bf D_C$ ) and the widths ( $\bf W_A$ ,  $\bf W_B$ ,  $\bf W_C$ ) of the integration windows are externally controlled by the user [Pro:07].

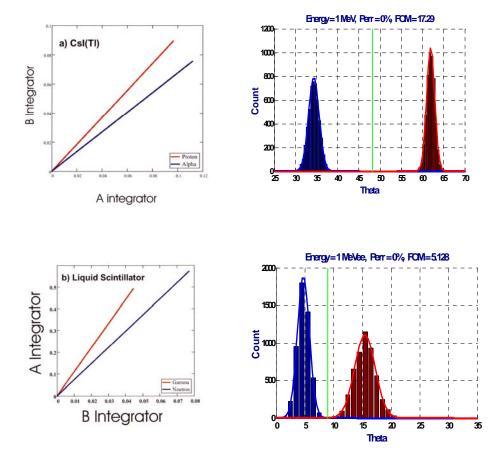

Figure 1.5 shows the simulated response to different pulse shapes for two different detector types. The plots on the left show standard "PSD" plots with average signals, while the plot on the right show the angle distributions from

simulations, with additive noise. Cleary, one is able to easily identify particle type using the PSD technique.

Figure 1.5: PSD plots demonstrating particle identification

The PSD8C chip's planned use, in basic NP experiments, is for: CsI(Tl) (charged particle ID), CsI(Na) ( $\gamma$ -ray spectroscopy with pile-up rejection and possible  $n/\gamma$  discrimination), and for BC-501A ( $n/\gamma$  discrimination). In all cases, the detector arrays have over 100 elements and the cost of conventional electronics is prohibitive.

While in basic science experiments, there is no problem with coupling the PSD8C chip with conventional power-hungry (VME) ADCs, the same cannot be said of DHS applications. Our group imagines an array of scintillators (e.g. CsI(Na), but perhaps ultimately a LaHalide detector) attached to the new generation of compact photomultiplier tubes (PMTs). The PSD8C chip just described, with a single ADC of the type described in this thesis integrated into the chip, along with a new generation of compact low-power CFD's would provide a compact, low-power and easily portable system suitable for homeland security applications

The PSD8C project is the first of two. The second project is to extend the CMOS-ASIC capability into the realm of extracting *full* pulse-shapes [Eng:07b]. While it is true that traditional DSP accomplishes this, traditional DSP is not transportable to a high-density, front-end CMOS ASIC. This is due to its need for fast (> 100 MSample/sec) many-bit digitizers (> 12 bits) in conventional DSP.

In principle, a signal waveform encodes (via a small set of signal parameters) what is truly important to the NP community. These are the answers to the: "what" (particle type), "where" (x,y,z) and "when" (t) questions. Using traditional DSP, the waveform is collected, digitized and stored over a long period of time. This is a digitization intensive operation that puts extreme demands on the downstream computation. Our group's proposed approach [Eng:07b] is to provide analog compaction on the front-end ASICs, analog storage of this information on the front-end ASIC, and then "slow" digitization with an on-chip ADC. In short, the ultimate "front-end" objective of this proposal is to push the analog CMOS possibilities as far as they can go in order to aid and simplify DSP operations.

We call our design to accomplish this goal "Analog-Assisted DSP" (AA-DSP) and its logic is shown in Figure 1.6. The proposed AA-DSP chip could be used to extract position information from a large segmented Ge or from pixilated CZT

detector array. This logic is an extension and improvement on that reported by Pullia et al. [Pul:00]. In order to characterize the waveforms, two sampling "round-robin" loops (per channel) are envisioned: a) A fast sampling loop used to extract parameters associated with the rise time of the primary CSA signal and total waveform of the induced signals; and b) a much slower sampling loop used to obtain multiple samples in the tail region of the primary CSA signal [Hal:07].

The timing logic (CFD + TVC) and the two banks of round-robin "integrate and hold" circuits (fast and slow) are fed by one of several CSA options. The adjectives fast and slow refer to the duration of time that each integrator is gated on. For our initial simulations, the (individual) period of integration is 62.5 ns in the fast bank and 500 ns in the slow bank. Simulations performed to date suggest that the proposed technique will be effective in capturing the desired waveforms.

Figure 1.6: AA-DSP logic

## **Need for On-Chip ADC**

Cleary, all three multi-channel ICs (HINP16C, PSD8C, and AA-DSP) discussed in the previous section could be enhanced by the addition of an on-chip ADC. The transmission of sensitive high-speed analog pulse trains to an off-chip VME ADC is a very difficult task. Low-level analog signals are easily corrupted. Moreover, even if the system is correctly designed, it is the nuclear physicists who set up and conduct the experiments. It is easy to degrade the performance of an analog system through improper grounding or shielding. The transmission of high-speed digital signals even over long distances is, on the other hand, relatively easy. Digital signals have high noise immunity.

Furthermore, VME ADCs are relatively expensive, large, and power-hungry. As described in an earlier section, it is important that systems proposed for use in nuclear threat detection systems to be used by DHS be compact and low-power. These attributes can only be achieved if an on-chip ADC is employed. Since the ICs described in the previous section are all fairy large (15 mm<sup>2</sup> – 50 mm<sup>2</sup>), the proposed ADC and companion RAM, used to store the digitized results, will increase the overall chip area (and chip costs) by only 10 – 30%.

In the case of HINP16C since there are 16 channels and two analog pulse streams ("Energy" and "Time"), a 2 MSample/sec converter could complete the digitization in a maximum of 16 µs. In addition to the ADC, a small 32 location, 18-bit wide memory (16 amplitude and 16 time values) is needed to store the results [Val:08]. Generally, only a small subset of the channels actually are impacted by radiation at any given time and need to be read out so the digitization would take even less time, typically just a few microseconds. Just like the currently used VME ADCs, the resolution of the on-chip converter need not exceed 12 bits.

For the PSD8C chip where there are 8 channels. Each channel consists of 3 sub-channels and a time-to-voltage converter (TVC). The digitization could once again be completed in a maximum of 16  $\mu$ s. As with HINP16C, only a small 32 location memory is needed to store the digitized values. Even for the AA-DSP chip with 8 channels the digitization could be completed in a maximum of 125  $\mu$ s (could be done in less time if multiple ADCs are used). Even in this case only a 256 location memory is required to store the data.

To minimize the system-level interconnect, we propose to transmit the contents of the RAM storing the ADC results back to a host computer via a serial "I2C-like" interface. This greatly simplifies the system level design and in particular the design of mother board and associated chip boards.

The on-chip ADC described in this thesis will be integrated for the first time in a second generation PSD8C chip. The IC is expected to be fabricated and ready for field testing by December 2009. The on-chip ADC presented in this thesis will then be used in the AA-DSP chip described in the previous section. While there are no immediate plans to integrate an on-chip ADC with HINP16C, this may well happen at some point in the future if funds for the integration were made available.

# Object and Scope of Thesis

The object of this thesis is to describe the design of an on-chip Analog-to-Digital Converter (ADC) suitable for integration with a series of custom ASICs developed or currently under development by our IC design research laboratory. The ASICs are intended for use in the detection of ionizing radiation in instruments intended for experiments in low- and intermediate-energy nuclear physics and (perhaps someday) in real-time homeland security nuclear threat detection

systems. The central features of the converter design include 12-bit resolution with a sampling rate of 2 MSamples/sec.

There are five chapters in this thesis. Brief descriptions of the ASICs which might benefit from the integration of an on-chip ADC were presented in this chapter along with a rationale for integrating the ADC into these custom chips in the future. In Chapter 2 we will compare several ADC architectures and provide justification for why a two-step flash technique was selected for integration. Moreover, a detailed description of the architecture and algorithm employed by the proposed two-step flash converter is provided. Chapter 3 discusses the design and performance of the many sub-components utilized in the ADC design. In Chapter 4 we present simulation results. The ADC was simulated at the behavioral level using MathCAD® and also at the electrical level using Cadence's Spectre® program. The MathCAD simulations were used to compare the results from the electrical simulations as part of the debugging process. Moreover, the effect of non-ideal behavior associated with the various sub-components was investigated using the simulator implemented in MathCAD®. Finally, Chapter 5 will give conclusions and discuss the future direction of this research work.

#### **CHAPTER 2**

#### ADC ARCHITECTURE

# **Comparison of ADC Architectures**

Analog-to-Digital Converter (ADC) architectures can be classified into two main categories based on the sampling rate of the input analog signal: 1) Nyquist-rate analog-to-digital converters b) Over-sampling analog-to-digital converters. If f<sub>B</sub> is the highest frequency of interest of the analog input signal and f<sub>S</sub> the frequency at which the analog input signal is sampled, then according to the Nyquist sampling theorem the sampling frequency f<sub>S</sub> must be at least twice the maximum input frequency, f<sub>B</sub>, in order to recover the signal from its samples. ADCs that operate with an input signal frequency close to the half the sampling frequency are called Nyquist-rate ADCs. This type of converter frequently require a very sharp cutoff for the preamplifier or anti-aliasing filter making it difficult and complex to implement [All:03].

ADCs that have input signal frequency much less than half the sampling frequency are called over-sampling ADCs. The anti-aliasing filter requirements of over-sampling ADCs are more relaxed than those of Nyquist-rate converters. The reason for this is that the sampling frequency is much higher than the Nyquist rate. The transition band that extends from the edge of the signal band to the edge of the smallest frequency band at which signals alias into the signal band is quite wide and the transition is smooth. A comparison of the frequency spectrum of a Nyquist-rate ADC and an over-sampling ADC is as shown in Figure 2.1 [All:03].

Figure 2.1: Frequency spectrum of Nyquist-rate ADC and over-sampling ADC

| Conversion rate                   | Nyquist-rate ADCs                                                                   | Over-sampled ADCs                                  |

|-----------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|

| Slow<br>(10-100<br>Samples/sec)   | Serial (ramp, dual-ramp). High resolution possible. (< 14 bits possible)            | Very high resolution possible (< 24 bits possible) |

| Medium<br>(1-100<br>KSamples/sec) | Successive approximation Algorithmic (< 16 bits possible)                           | Moderate resolution<br>(< 18 bits possible)        |

| Fast (1 – 100 MS/sec)             | Flash<br>Multiple-bit pipeline<br>Folding and interpolating<br>(< 14 bits possible) | Low resolution<br>(< 6 bits possible)              |

Table 2.1: Classification of ADC architectures

Within the two major classes of converters, there are many subclassifications. Table 2.1[All:03] presents the classification of various types of ADCs along with their resolution and conversion rates. Based on the earlier description it is easy to understand that the fastest converters are those of the Nyquist class. When high sample rates and resolution are needed, Nyquist-rate converters still rule! In "slow" and "medium" speed applications, the over-sampling converters dominate. In over-sampling converters, "resolution in time" is traded in for "resolution in amplitude". Over-sampling converters are very popular because they require relatively low-performance analog sub-systems where both matching and offsets requirements are easily met.

Among the fastest of the converters are those generally referred to as "flash" or "parallel" ADCs. In "flash" converters, the input voltage is compared against 2<sup>N</sup> (where N is the number of bits of resolution desired) voltages linearly spaced across the full-scale range of the converter. The comparator output generate a "thermometer" encoded output which is in turn converted to a binary encoded output. Note for a N-bit conversion, 2<sup>N</sup> analog comparators are required.

While flash converters are capable of very high sampling rates, the associated hardware is very large when high resolution (> 8 bits) is required. In this research we selected a "folding" ADC [All:03]. In a folding ADC the full-scale range is subdivided into P sub-ranges. Each of the P subranges is mapped into a single subrange. A "coarse" converter determines in which of the P subranges the input signal lies. The input signal is then mapped into the aforementioned single subrange. A "fine" quantizer then acts on this range to determine the appropriate fine bits. When this process occurs over two clock cycles, the resulting ADC is called a "two-step" ADC. In the next section, we discuss two-step flash converters.

## **Two-Step Flash Converter**

Two-step (sometime referred to as "two-stage" or "half-flash") flash architectures are an effective means of realizing high-speed, high-resolution analog-to-digital converters because they can be implemented without the need for operational amplifiers having either high gain, large gain-bandwidth product, or a large output swing. Moreover, with conversion rates approaching half those achievable by fully parallel designs, half-flash architectures provide both a relatively small input capacitance and lower power dissipation than their full-flash relatives [Raz:92].

As discussed in Chapter 1, an ADC suitable for integration on the various ICs under development should be capable of 12-bit resolution and a sampling rate of a few MSamples per second. The design described in this thesis is based on an earlier design by Wooley and Razavi [Raz:92]. In the sections that follow we will describe our design and the manner in which in differs from the Wooley converter. The designs are very similar at the architectural. Significant differences exist in how the circuits are clocked an in the implementation details at the circuit level.

The main advantage of using a two-step flash converter over a fully parallel converter in the proposed application is the reduction in the number of comparators used. For example, a fully parallel 12-bit ADC would require 2<sup>12</sup> (4096) comparators where a two-step flash ADC (7-bit first stage and 6 bit second stage) requires on 128 comparators in the first stage and 64 comparators in the second stage (a total of just 192 analog comparators). Thus, use of a two-step flash ADC results in substantial reduction in the number of comparators. The proposed two-step flash ADC has a 7-bit first stage that produces a "coarse" estimate of the input analog voltage. The 6-bit second stage then uses this "coarse" estimate to

produce a "fine" estimate of the input analog voltage. Digital correction logic is then used to combine the two estimated in order to produce the desired 12-bit result.

One bit of redundancy or overlap is used in the proposed architecture to enable the second stage to correct for out-of-range errors in the first-stage (resulting from mismatch errors), thereby relaxing the precision required of the first-stage comparators. The use of a fully-differential (differential input AND differential output) architecture increases the input dynamic range, eliminates even-order harmonic distortion, and suppresses common-mode noise due to supply transients and noise coupling via the substrate [Raz:92]

The ADC is designed with an input range of -1.2 Volts to 1.2 Volts relative to the analog signal ground, which we call AGND. The AGND voltage in our design is 2.4 Volts. Therefore, the effective input range of the ADC is from 1.2 Volts to 3.6 Volts. This range is exactly what is needed for both the amplitude and time pulse trains currently produced by the ICs discussed in Chapter 1 of this thesis. The ADC is designed such that it produces a 12-bit zero output for an effective input analog voltage of 1.2 Volts (approximate bandgap voltage) and a 12-bit all ones output for an effective input analog voltage of 3.6 Volts (3 X bandgap voltage). The digital output word could easily be converted to a twos-complement representation if it proves more convenient.

# Two-Step Algorithm

The two-step algorithm that is used in the ADC architecture is as shown in Figure 2.2. We will describe the algorithm [Raz:92] in detail in this section of the thesis.

Figure 2.2: ADC converter architecture

As illustrated in Figure 2.2, the input analog voltage, V<sub>in</sub>, is applied to the first stage of the ADC. The first stage produces a "coarse" digital output for the applied input analog voltage. The 7-bit coarse digital output is then passed to a 7-bit switched-capacitor (SC) Digital-to-analog converter (DAC) which produces an analog estimate of the "coarse" value. This analog estimate of the "coarse" code is then subtracted from the input analog voltage by the subtractor (which we refer to as the "residue generator" in the remainder of this thesis) in order to produce the "residue". The "residue" voltage is then passed, as an analog input, to the second stage of the converter. The second stage is a 6-bit flash ADC that produces a "fine" digital output for the applied "residue" voltage.

The 7-bit coarse digital output is passed through a delay register (not shown in the figure) and then to the digital correction logic circuit where it is combined with the 6-bit fine digital output of the second stage to produce the 12-bit final digital output. Details on how the two digital values are combined to form a single 12-bit digital word will be presented in a later section of this thesis.

#### First Stage

A block diagram of the first-stage electronics is shown in Figure 2.3.

Figure 2.3: Block diagram of first-stage electronics

The first stage of the ADC is composed of a resistive ladder, an array of 128 comparators, a SC DAC, a residue generator and a thermometer- to-binary converter. In order to differentiate the first-stage components from the components of the second stage a prefix 'first stage' is added to the comparators

and the resistor ladder. The first-stage resistor ladder consists of  $2^7$  (128) identical resistors. One end of the first-stage ladder is connected to  $V_{Ref\_plus}$  (3.6 Volts) terminal and the other to  $V_{ref\_minus}$  (1.2 Volts). The first-stage ladder divides the full-scale range (2.4 Volts) into 128 equal steps (stepsize is 18.75 mV). The tap voltages from the first-stage resistor ladder are used as one of the inputs to the first-stage comparators with the other input to each of the first-stage comparator coming from the analog input voltage,  $V_{in}$ .

A first-stage comparator produces a 'one' if the applied tap voltage is greater than the analog input voltage, V<sub>in</sub>, else it produces a 'zero'. Thus the array of 128 first-stage comparators produces a 128-bit "thermometer" code. This 128-bit code is then sent to a thermometer-to-binary converter where it is encoded into the 7-bit (coarse) estimate. The 128-bit thermometer code also drives a switched-capacitor DAC, which produces an analog approximation of the thermometer code. The analog approximation produced by the DAC is subtracted from the analog input voltage, V<sub>in</sub> to obtain the "residue". The first stage comparators, DAC, and residue generator are all implemented as fully differential circuits.

#### **Second Stage**

The block diagram of the second-stage electronics is shown in Figure 2.4. The second (or "fine") stage digitizes the differential output of the residue generator to encode the six least significant bits (fine) of the ADC. The second-stage consists of a resistive ladder with a ladder loading correction circuit, an array of 64 comparators, and a thermometer-to-binary converter.

The second-stage ladder consists of 128 identical resistors that are connected across four resistors of the first stage ladder near its mid-point. Recall that the first-stage ladder divides the full-scale range (2.4 V) into 128 equal

segments with each segment 32 LSBs (Least Significant Bits) wide or 18.75 mV. A LSB equals  $\frac{2.4}{2^{12}}$  Volts or 586  $\mu$ V. The second- stage has a full-scale (FS) range of 128 LSBs *i.e.* 75 mV. Therefore, the second-stage ladder is connected across four first-stage ladder resistor segments.

Figure 2.4: Block diagram of second-stage electronics

The loading introduced by the second-stage ladder upon the first-stage ladder introduces a systematic error. This error can be eliminated by cancelling the currents drawn from the first-stage ladder by the second-stage ladder. This is done by injecting currents equal to those drawn by the second stage ladder at the junction of the two ladders [Raz:92].

The tap voltages from the second-stage resistor ladder are applied as one of the inputs to the second stage comparators, the other input, applied to all of the second-stage comparators, is the residue voltage from the first stage. A preamplifier, A<sub>1</sub>, with a gain of approximately 14 (considerably larger than the value of 3 used in the original Wooley [Raz:92] design) is used to amplify the differential 'residue' input which varies from 1 to 64 LSB (*i.e.* from 585 mV to 37.5 mV). This is necessary to prevent the signal integrity of the differential 'residue' input from being lost due to the offset voltage of second stage comparator or charge injection from the switches.

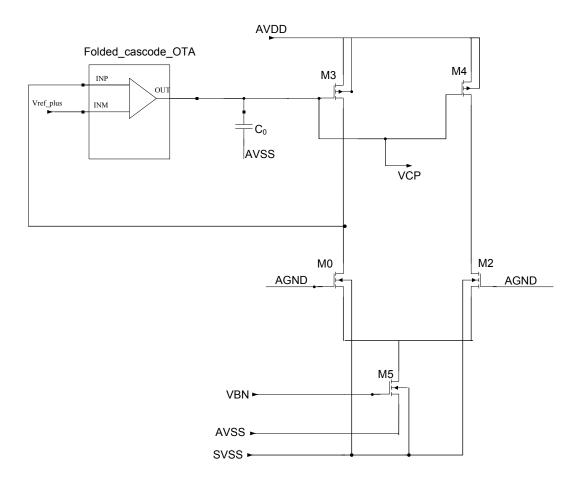

The gain control circuit produces a control voltage for the preamplifier,  $A_1$ , to ensure a gain which is insensitive to process corner. As will be explained in more detail later, the control voltage automatically adjusts the gain as process parameters vary. This novel pre-amplifier design developed as part of this research will be described in more detail in a later section of this thesis.

The second-stage comparators produces a 'one' if the applied tap voltage is greater than the residue voltage else it produces a 'zero'. Thus, the array of 64 second-stage comparators produces a 64-bit thermometer code. This code is then applied to a thermometer-to-binary converter where it is encoded into the 6-bit (fine) value which is then passed on to the digital correction logic.

# System Timing

The system timing of the ADC is as shown in Figure 2.5 and is somewhat different from that employed by Wooly *et. al.* The operation of the individual components in the ADC is controlled by three non-overlapping mutually exclusive clocks  $\emptyset_1$ ,  $\emptyset_2$ ,  $\emptyset_3$ . Mutually exclusive implies that at any given time only one of the three clocks is high. The entire operation of the ADC is pipelined (unlike the original

design) and is completed in two clock periods. A clock period is defined as a single occurrence of all the three clock phases:  $\emptyset_1$ ,  $\emptyset_2$ ,  $\emptyset_3$ . The design of the three-phase clock generator is beyond the scope of this thesis. A VerilogA model of the generator was used in all electrical simulations of the ADC presented in Chapter 4.

Since the analog pulse trains associated with the various radiation detection ICs discussed in Chapter 1 will always be digitized as a block, the pipelined behavior has a negligible impact on overall system performance adding only one additional clock cycle to the time required to digitize the block of analog voltages. The use of pipelining; however, allows for longer settling times associated with the aforementioned analog sub-systems and also simplifies the timing constraints. Wooley's design depended upon small, reasonably well-controlled delays in order to ensure proper operation of many of the analog sub-systems. Here we only require that the clocks be non-overlapping. We will assume a master clock frequency of 5 MHz (200 nsec clock period) for convenience. This implies that the duration of each of the three phases is 67 nsec. This applies an output sample rate of 1.7 MSamples/sec. The operation of the ADC is explained below with the help of Figure 2.5. Note, a new input voltage to the ADC should be applied at the start of  $\emptyset_2$ .

During  $\emptyset_1$ , the first-stage resistor ladder tap voltages are sampled by the first-stage comparator circuits. Offset-cancellation in the first-stage comparators also takes place during  $\emptyset_1$ . The analog input voltage,  $V_{in}$ , is then sampled by the first-stage comparators during  $\emptyset_2$ . The first-stage comparators compare the first-stage ladder tap voltages with the sampled input voltage and produce either a 'one' or a 'zero' based on their inputs. The first-stage comparators make their "decision" during  $\emptyset_3$ . The outputs from the first-stage comparator are latched on the falling edge of  $\emptyset_3$ .

Input voltage, Vin, should change on Ø2. OS cancel and Sample 1<sup>st</sup> stage ladder Ø1 sample Vin Ø2 1<sup>st</sup> stage comparators Compare Comparator outputs stored in latch Ø3 Ø1 ✓ Reset DAC DAC Ø2 ✓ Update DAC Ø3 Sample Vin Ø1 ✓ Subtractor holds residue Subtractor Ø2 Sample DAC and offset cancel Ø3 OS cancel and sample subtractor output Ø1 Sample second stage ladder 2<sup>nd</sup> stage comparators Ø2 Compare Comparator outputs stored in latch Ø3

Figure 2.5: System timing diagram

The digital-to-analog converter (DAC) is reset during  $\emptyset_2$  and its value is updated based on the first stage comparator's output during  $\emptyset_3$ . This implies that the time it takes for the first-stage comparators to resolve (not long because of the positive feedback that is employed) plus the time it takes for the DAC outputs to resolve must not exceed 67 nsec. The residue generator (subtractor circuit) samples the DAC output during  $\emptyset_3$ . Offset cancellation of the residue generator output also takes place during  $\emptyset_3$ . The residue generator samples the input voltage,  $V_{in}$ , and subtracts the DAC output voltage from it producing the 'residue' during  $\emptyset_1$  of the next clock period. The subtractor circuit has 67 nsec to settle. The subtractor holds this residue during  $\emptyset_2$ .

Offset-cancellation of the second-stage comparators takes place during  $\emptyset_1$ . The comparators also sample the residue generator output during  $\emptyset_1$ . The second-stage ladder tap voltages are sampled by the second-stage comparators during  $\emptyset_2$ . The second stage comparators produce either a 'one' or a 'zero' based on their inputs during  $\emptyset_3$ . Note: the second-stage comparator outputs are delayed from the first-stage comparator outputs (because of the pipelining) by one full clock period. The "fine" and "coarse" codes are aligned in the digital correction logic by delaying the "fine" code by one register delay.

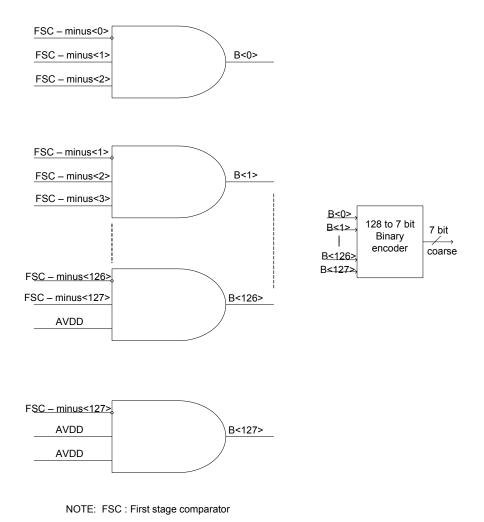

### **Digital Encoding**

Digital encoding performs the function of converting the thermometer code outputs of the comparators into a binary code. The design of the digital encoding and correction logic (at the circuit-level) is beyond the scope of this thesis. The logic-level design will now be described. VerilogA code was used to implement the digital encoding and correction logic in the electrical simulations presented in Chapter 4.

The digital encoding is used to obtain a 7-bit "coarse" output from the first stage and a 6-bit "fine" output from the second stage. These binary outputs are then corrected digitally to obtain the 12-bit ADC output. The encoding logic used in this ADC consists of a series of AND gates followed by an encoder. The digital encoding can be modified to correct out of order 'ones' and 'zeros' caused by large offsets in the comparators by sensing three adjacent levels in the thermometer code [ Raz:92].

# Redundancy and Digital Correction Algorithm

The first-stage comparators are designed for high-speed and modest resolution, while potential moderate errors are accommodated by using one bit of overlap between the two stages [Raz:92]. The overlap makes sure that the residue (difference between V<sub>in</sub> and the DAC output voltage) of the first stage falls within the input range of the second stage. With ideal comparators and reference voltages, the first-stage output changes for input transitions that are integer multiples of 32 LSBs. The residue would then vary from 0 to a maximum of 32 LSBs, and the second stage would need a quantization range of 32 LSBs, that is a resolution of 5 bits.

Let us suppose that the  $j^{th}$  comparator in the first stage has an offset of 'deltaV<sub>j</sub>', then the code transition threshold corresponding to a V<sub>in</sub> of (32LSB)\*j is shifted by 'deltaV<sub>i</sub>'.

As shown in Figure 2.6 where the  $j^{th}$  and  $(j+1)^{th}$  comparators have offsets  $deltaV_j(<0)$  and  $deltaV_{j+1}(>0)$ , the residue varies from  $deltaV_j$  to  $(32LSB)+deltaV_{j+1}$ .

Figure 2.6: Residue versus input voltage

Therefore, an input range of 32 LSBs in the second stage is not sufficient to digitize the residue. The 12-bit ADC is assumed to have a first-stage comparator offset that never exceeds 16 LSBs (9.3 mV). As we shall demonstrate later, out first-stage comparators were designed to have input-referred offsets considerably smaller than this value ( $3\sigma$  offset of 1 - 2 mV). The second stage is designed for a resolution of 6 bits in order to digitize a residue as large as 64 LSBs. This value provides a buffer of +/- 16 LSBs as we shall now demonstrate.

As shown in Figure 2.7, the residue from the first stage is shifted up by 16 LSBs, so that as long as offsets from the j and (j+1) comparators in the first stage are less than 16 LSBs, the residue falls within the input range of the second stage *i.e.* 64 LSBs. In order to shift the residue up by 16 LSBs, the analog output of the DAC is shifted down by 16 LSBs.

Figure 2.7: Range expansion in A/D converter

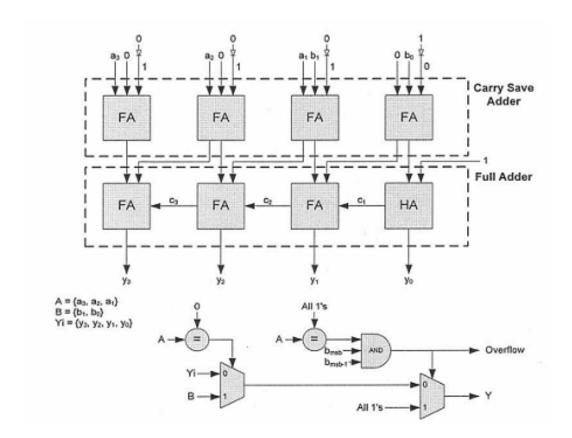

The digital outputs of the two stages of the ADC are added using the digital correction logic to obtain the final 12-bit output of the ADC. The digital correction algorithm is depicted in Figure 2.8

Figure 2.8: Digital correction algorithm flowchart

The algorithm first checks the 7-bit digital output from the first stage, if it is zero, the entire output of the first stage is shifted to the left by five places and the

6-bit second stage output of the ADC is added to the first-stage output to get the 12-bit final output. If the output of the first stage is not zero, we shift it to the left by five places and shift it down by 16 LSBs. This is done to emulate shifting the DAC output down by 16 LSBs. The 6-bit second stage output of the ADC is then added to the first stage output to get the 12-bit final output.

#### CHAPTER 3

#### **DESIGN OF SUB-SYSTEMS**

The ADC described thus far is comprised of two stages with each stage consisting of various analog sub-systems: analog comparators, resistor ladders, a digital-to-analog converter (DAC), and a switched-capacitor (SC) subtractor. The target technology is the AMIS 0.5 micron, NWELL process (C5N). The process supports three metal layers, double-poly capacitors, and a high resistance poly layer. The C5N process is a 5 Volt process.

The circuits described in this chapter were designed assuming the (nominal) process parameters shown below:

$V_{TN}$  is threshold voltage of NFET = 0.75 Volts

$V_{TP}$  is threshold voltage of PFET = -1 Volts

$K_{PN}$  is transconductance parameter of NFET = 100  $\mu A/V^2$

$K_{PP}$  is transconductance parameter of PFET = 32  $\mu A/V^2$

$K_{aN}$  is 1/f noise parameter for NFET = 6.3 x 10<sup>-26</sup> A F [Lee:02], [OCo:99]

$K_{aN}$  is 1/f noise parameter for PFET = 3.8 x 10<sup>-30</sup> A F

## Single-Ended to Differential Converter

Single-ended signaling is a method of transmitting signals where one wire carries a voltage that represents the signal. Differential signaling is a method of transmitting signals by means of two complementary signals sent on two separate wires. The main disadvantage of single-ended signaling is that it lacks the ability to reject noise caused by differences in ground voltage level and any noise that may be picked up on the signal wire. This is because single ended method relies on the absolute value of the voltage carried by the wire to represent the signal whereas a

fully-differential method relies only on the absolute difference between the two complimentary voltages to represent the signal. Thus, any noise affecting both the wires is cancelled out when taking the difference.

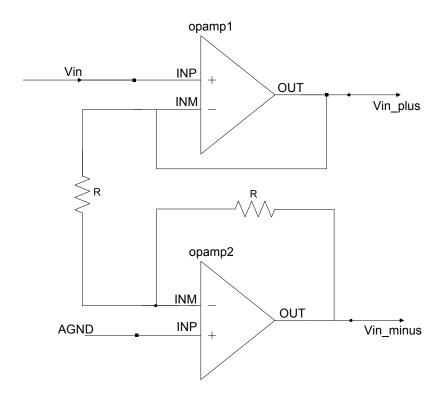

Since the analog output pulse trains from the ICs discussed in Chapter 1 are single-ended but the ADC is fully-differential, a single-ended-to-differential conversion must be performed. The single-ended-to-differential converter as the name suggest converts a single-ended input voltage into a fully differential voltage with respect to an analog ground (in our case AGND, 2.4 Volts). The singled-ended-to-differential conversion circuit is comprised of two operational amplifiers. One operational amplifier is connected as a unity-gain follower while the second as an inverting gain amplifier with a gain of -1 as shown in Figure 3.1. The value for R is  $30~\mathrm{k}\Omega$  and is implemented with the HY resistor layer (doped poly2 layer with a sheet resistance of 1 k $\Omega$  per square).

Figure 3.1: Single-ended-to-differential conversion circuit

The input  $V_{in}$  is applied to the top operational amplifier which is in a unity gain configuration to obtain  $V_{in\_plus}$  and to the bottom operational amplifier which is in an inverting configuration in order to obtain  $V_{in\_minus}$ . The output is fully-differential and centered about AGND. While the circuit was simulated and its performance was consistent with expectations, no effort was made to actually integrate the circuit into the ADC design at this time. Single-ended-to-differential conversion was performed using VerilogA for the electrical simulations described in Chapter 4. Several of the ADC sub-systems are yet to be designed and were modeled using VerilogA. The VerilogA code can be found in Appendix A.

# Core operational amplifier

The core operational amplifier used in this circuit is a two-stage design [Hog:94]. The first stage is a folded cascade and the second stage is a class AB output stage. The class AB output stage is a complementary common-source amplifier where the NFET serves as the load for the PFET and vice versa.

The core operational amplifier meets the following specifications. The GBW is approximately 50 MHZ. It is capable of output currents of several milli-amps and possesses a near rail-to-rail output voltage swing. The slew rate of the amplifier is approximately 10 Volts/µsec. The core amplifier was not designed by the author; but rather, was designed for the PSD8C IC described in Chapter 1. A more detailed description can be found in [Pro:07].

## **Reference Generator**

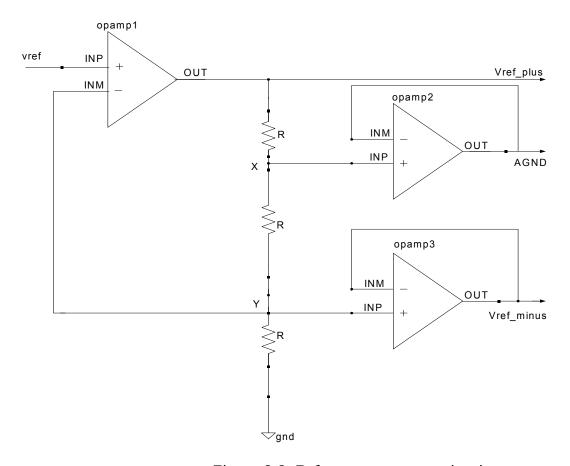

The reference generator provides the ADC with three reference voltages:  $(V_{ref\_plus}, V_{ref\_minus}, \text{ and AGND})$ . As shown in Figure 3.2, the circuit employs three

operational amplifiers. The core amplifier is the same as the one used in the single-ended-to-differential converter circuit. All the resistors used in the circuit are of the HY type. All the resistors have a value of  $30K\Omega$ .

Figure 3.2: Reference generator circuit

The non inverting terminal of operational amplifier 1 is fed with a bandgap voltage  $V_{REF}$  (approximately 1.2 Volts) that is obtained from the 'FULL\_BIAS' circuit of the PSD-8C chip. For more details on the biasing circuits, the reader is referred to [Pro:07] and [Sad:02].

The operational amplifier (OpAmp 1) is in a non inverting configuration and its output voltage is given as  $V_{ref\_plus} = V_{REF}(1 + \frac{R_2}{R_1})$ . Where  $R_2 = 2R$ . and  $R_1 = R$ , resulting in  $V_{ref\_plus}$  of 3.6V. OpAmp 2 and OpAmp 3 are voltage followers, and they

buffer the voltages at points X and Y. Since all three resistors are equal, the drop across each resistor is the same resulting in the voltages at points X and Y being 2.4 Volts and 1.2 Volts respectively. Thus, AGND is 2.4 Volts, and  $V_{ref\_minus}$  is 1.2 Volts.

While the circuit was simulated and its performance was consistent with expectations, no effort was made to actually integrate the reference generator circuit into the overall ADC design at this time. Single-ended-to-differential conversion was performed using a VerilogA model in the electrical simulations described in Chapter 4. A more detailed characterization of its performance is needed before the circuit will be integrated into the overall ADC design.

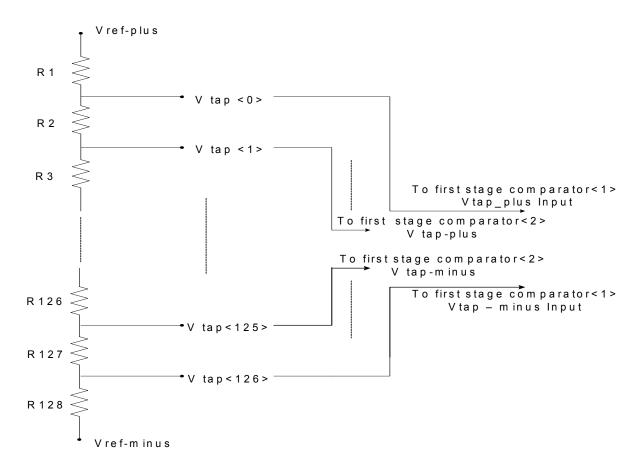

# First Stage Ladder

The first-stage ladder circuit is used to divide the full-scale range (2.4 Volts) of the ADC into 128 differential voltages that vary in steps of 32 LSBs. As shown in Figure 3.3 each resistor in the ladder is constructed from "NY" poly. A "NY" resistor is made of a *undoped* poly II layer. The NY sheet resistance is nominally  $50\Omega/\text{square}$ . Based on [Raz:92], a value of 40  $\Omega$  was chosen. A length of  $10\,\mu\,\text{m}$  and a width of 12.5  $\mu\,\text{m}$  is used for each NY resistor in the ladder. Based on information from the fabricator, we feel these values will yield acceptable matching characteristics (on the order of 0.5 %). The total resistance of the ladder is 5.12 k $\Omega$ . This means that the ladder dissipate 1.1 mW of power. Due to process variations, the ladder resistance is likely to vary by +/- 20 percent.

If the input capacitance for a first-stage comparator is on the order of 100 fF then for a tap near the center of the ladder the associated time constant,  $\tau$ , is equal to 512 ps. Since ten time constants provide more than sufficient time for voltages

settle to the 12-bit level, the tap voltages applied to the comparators should become stable in less than 5 nsec (which is a small fraction of the 67 nsec associated with a single phase of the clock). Figure 3.3 illustrates the way in which the tap voltages are applied as differential pairs to the first stage comparators.

Figure 3.3: First-stage ladder circuit

# First Stage Comparator

The performance of the first-stage comparator plays a crucial role in overall system performance. The input-offset of the first-stage comparator must be well within the error range covered by the redundancy and digital correction as was discussed in the previous chapter. With a one bit redundancy this range is approximately 9.4 mV for a differential input range of 2.4 Volts.

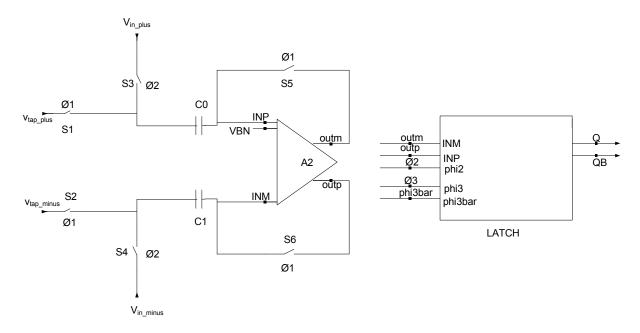

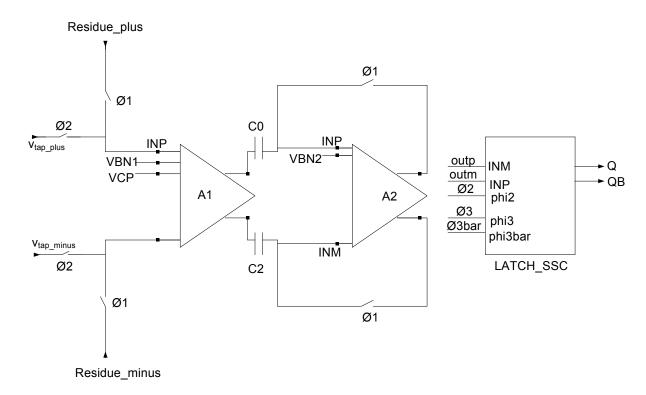

Figure 3.4 presents a block diagram of the first-stage comparator design. The block diagram of Figure 3.4 is provided to make it easier for the reader to understand how the overall comparator operates. The design consists of an offset-compensating preamplifier (gain of approximately 5) followed by a latch. In Wooley's [Raz:92] design, upon which ours is based, the pre-amplifier and latch operations were merged. While this reduces transistor count, it complicates the design to some extent.

The switches  $S_1$ - $S_4$  are used to sample the differential input voltage and the differential first-stage resistor ladder tap voltages. During  $\mathcal{O}_1$ , the resistor ladder tap voltages are sampled. The preamplifier is forced into the offset cancellation mode when switches  $S_5$  and  $S_6$  are closed during  $\mathcal{O}_1$ . The preamplifier is designed such that it idles at 1/3 <sup>rd</sup> of the supply voltage during offset cancellation mode. The offset cancellation is not perfect but reduces the offset by a factor of (gain+ 1) which is 6 in this design. During  $\mathcal{O}_2$  the differential input voltage is applied to capacitors  $C_0$  and  $C_1$ .

The preamplifier amplifies the difference between the tap voltages applied in  $\emptyset_1$  and differential input voltages applied during  $\emptyset_2$  i.e. ( $V_{ref\_plus}-V_{in\_plus}$ ) and ( $V_{ref\_minus}-V_{in\_minus}$ ) and produces two outputs 'outp' and 'outm'. The outputs 'outp' and 'outm' are then applied to the latch in  $\emptyset_3$  to get the final output of the first stage comparator. The latch is also designed to hold the comparator output during  $\emptyset_1$ .

Figure 3.5 shows the first stage comparator schematic. The first-stage schematic is designed to discriminate voltage differences as small as 2 mV and to settle within 25 nanoseconds. The sizes of all the transistors used in the above schematic are as shown in Table 3.1. Devices  $M_1$ - $M_4$  and  $M_{10}$  constitute the preamplifier. The bias current through device  $M_{10}$  is 50  $\mu$ A. FETs  $M_5$ ,  $M_6$ ,  $M_8$ , and  $M_9$

form the latch. Further work is needed to make sure the input-referred offset is sufficiently small but the offset is estimated at about 2 mV.

Figure 3.4: First-stage comparator block diagram

| Transistor | Туре | Width(µm) | Length(µm) | Multiplier |

|------------|------|-----------|------------|------------|

| M1         | n    | 1.6       | 0.6        | 1          |

| M2         | n    | 1.6       | 0.6        | 1          |

| М3         | р    | 1.7       | 2.9        | 1          |

| M4         | р    | 1.7       | 2.9        | 1          |

| M5         | р    | 1.9       | 2.8        | 1          |

| M6         | р    | 1.9       | 2.8        | 1          |

| M8         | n    | 1.9       | 9.6        | 1          |

| M9         | n    | 1.9       | 9.6        | 1          |

| M10        | n    | 6.4       | 2          | 1          |

| M11        | р    | 3.1       | 0.6        | 1          |

| M12        | р    | 3.1       | 0.6        | 1          |

| M13        | n    | 0.9       | 0.6        | 1          |

| M14        | n    | 0.9       | 0.6        | 1          |

| M15        | n    | 0.9       | 0.6        | 1          |

| M16        | n    | 0.9       | 0.6        | 1          |

| M17        | n    | 0.9       | 0.6        | 1          |

| M18        | n    | 0.9       | 0.6        | 1          |

| M19        | n    | 0.9       | 0.6        | 1          |

Table 3.1: Transistor sizes for first-stage comparator schematic

Figure 3.5: First-stage comparator schematic.

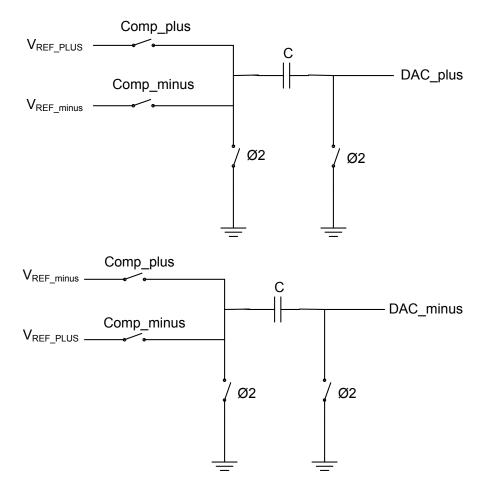

# **Digital-to-Analog Converter**

The ADC's first-stage comparators produce a thermometer code output which leads us to use a "linear" or "segmented" capacitor array for the Digital to Analog Converter (DAC) that can be driven directly by the outputs of the first-stage comparators. The linear capacitor array DAC has many advantages; for example, it avoids the need to convert the thermometer code output of the first stage comparators into a binary code, thereby increasing the speed of the ADC. Using a

linear array capacitor DAC ensures a monotonic transfer characteristics of the DAC [Raz:92]. A linear array DAC is also easy to layout.

The DAC used in the ADC is fully-differential and is made of two arrays of DAC unit capacitors. The DAC\_PLUS array consists of 128 DAC\_PLUS unit capacitors (1 pF) and produces the DAC\_PLUS output. Similarly, the DAC\_MINUS array consists of 128 DAC\_MINUS unit capacitors (C<sub>U</sub>) and produces the DAC\_MINUS output. In the array the top plate of the capacitors in all the unit cells are tied together. Both DAC\_PLUS and DAC\_MINUS arrays are driven by the first-stage comparator outputs. In order to shift the DAC output down by 1/2 LSB, as described in Chapter 2, the capacitor driven by the very first comparator in the array was made 0.5 pF or one-half the size of the unit capacitor used in the remainder of the array.

Figure 3.6 shows the DAC unit cell. The DAC is reset during  $\emptyset_2$  and updated during  $\emptyset_3$ . The operation of both of the unit cells is identical except that they are switched to different reference voltages based on the first-stage comparator's complimentary outputs.

Let us consider the first DAC\_PLUS unit cell in the DAC\_PLUS array. If the Comp\_plus output of the first comparator in the first stage is a 'one' then the bottom plate of the capacitor in the first unit cell is switched to  $V_{ref\_plus}$  else it is switched to  $V_{ref\_minus}$ . Similarly, if the output of the second comparator in the first stage is a 'one' then the bottom plate of the capacitor in the second unit cell is switched to  $V_{ref\_plus}$  else it is switched to  $V_{ref\_minus}$ . By switching some of the capacitors to the positive reference and others to the negative reference, a capacitor voltage divider is formed.

Thus if 'sumk<sub>k</sub>' capacitors out of the total ' $C_{TOTAL}$ ' are connected to  $V_{ref\_plus}$  in the DAC\_PLUS then its output voltage is given as :

$$\begin{aligned} \text{DAC\_plus} &= & \frac{ [\text{Vref\_plus} - \text{Vref\_minus}] * \text{sumk}_k + [\text{Vref\_minus}] * C_{\text{TOTAL}} + V_{AGND} * (\frac{C_U}{2}) }{ C_{TOTAL} + (\frac{C_U}{2}) } \end{aligned}$$

The DAC\_MINUS array also functions in a similar manner except that when  $Comp\_plus\ output\ of\ the\ first\ comparator\ is\ a\ 'one'\ then\ the\ bottom\ plate\ of\ the$  capacitor in the first unit cell is switched to  $V_{ref\_minus}$  else it is switched to  $V_{ref\_plus}$ .

Figure 3.6: DAC unit cell

The switches that connect the bottom plate of the capacitor to the reference voltages are transmission gates (rather than a single FET). This is necessary to pass both high and low voltages easily. The FETs comprising the switches are

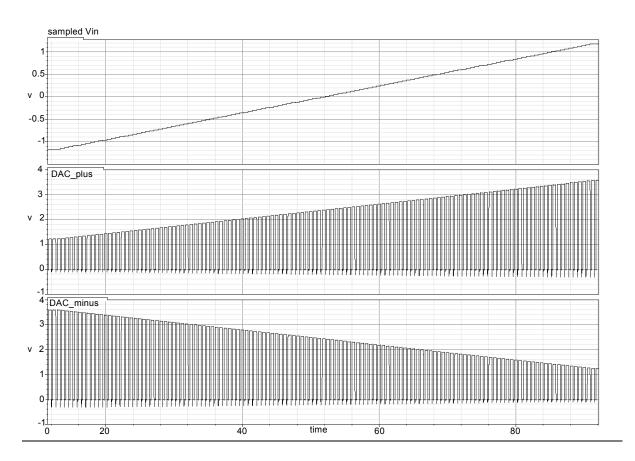

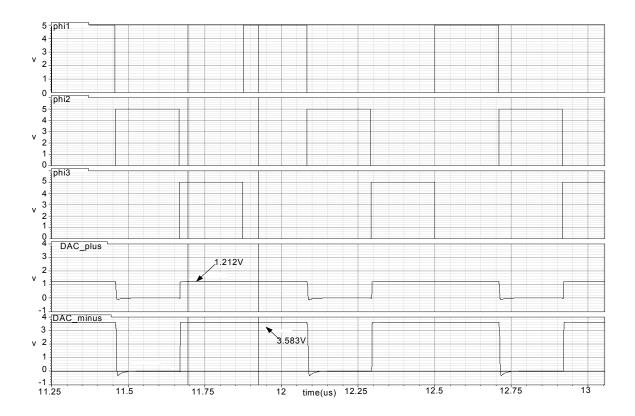

made wider in order to achieve a fast settling time in the DAC. However, the 'reset' switch used during  $\emptyset_2$  is a single NFET with minimum area so as to decrease the effect of charge injection on the DAC and to minimize the parasitic capacitance on the DAC output nodes. The DAC output voltages are very sensitive to parasitic capacitance on the output node. Figure 3.7 illustrates the DAC\_plus and DAC\_minus outputs' ramp response.

The transfer characteristics of the DAC can be seen in Figure 3.8. As illustrated in the figure, the DAC\_plus and DAC\_minus settle to their final value within 20 nanoseconds. The plots presented below are characteristics of DAC when it was simulated using the typical process corner.

Figure 3.7: DAC\_plus and DAC\_minus outputs of a ramp input

Figure 3.8: DAC transfer characteristic

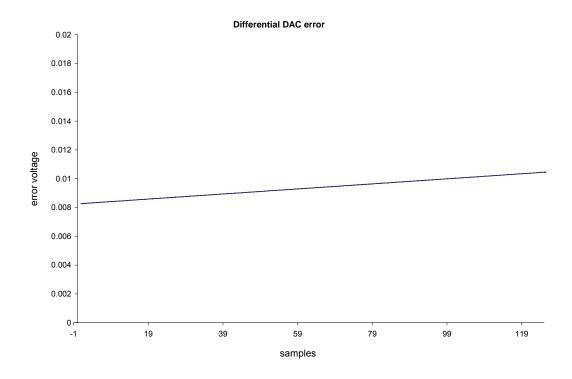

Figure 3.9: Differential DAC error plot

Figure 3.9 shows the differential DAC error simulated with the typical process corner model. The differential DAC error is the difference between the ideal DAC\_plus output minus the obtained DAC\_plus output and ideal DAC\_minus output minus the obtained DAC\_minus output.

Note that the DAC differential error is almost constant, with a maximum variation of +/-1mV due to non-ideal effects; for example, charge injection. It is larger than desired and efforts are still underway to reduce it. The use of larger unit capacitors (currently the unit capacitor is 1 pF) is being tried.

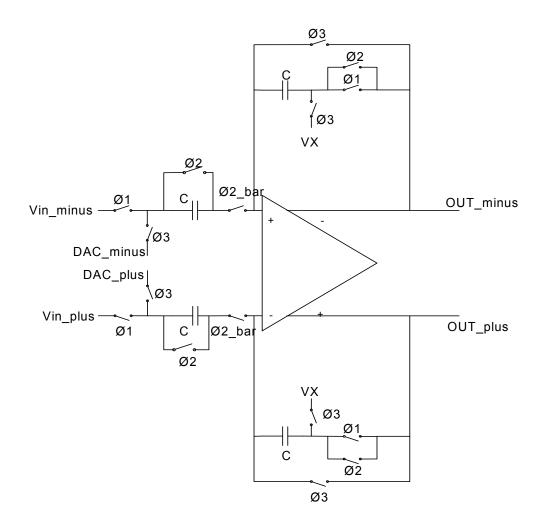

#### Residue Generator

The residue generator is used to obtain the difference between the analog input voltage  $V_{in}$  and the analog voltage generated by the DAC. This difference voltage is referred to as the 'residue'. Figure 3.10 depicts the residue generator circuit. The circuit includes offset-cancellation unlike the subtractor used in [Raz:92]. The capacitors in the figure are one-half the size of the unit capacitors in the DAC *i.e.* 0.5 pF. The residue generator is implemented in a fully differential manner; therefore, it produces Residue\_plus and Residue\_minus outputs which as stated are the difference between  $V_{in\_plus}$  and DAC\_plus and  $V_{in\_minus}$  and DAC\_minus respectively.

The transient response of the residue generator depends on the OTA (Operational Transconductance Amplifier) performance used in its implementation. The input voltages  $V_{in\_plus}$  and  $V_{in\_minus}$  are sampled in during  $\emptyset_1$ . The DAC\_plus and DAC\_minus voltages are sampled during  $\emptyset_3$  of the previous clock period (recall the use of pipelining described in the previous chapter). The residue that is generated during  $\emptyset_1$  is then held during  $\emptyset_2$ .

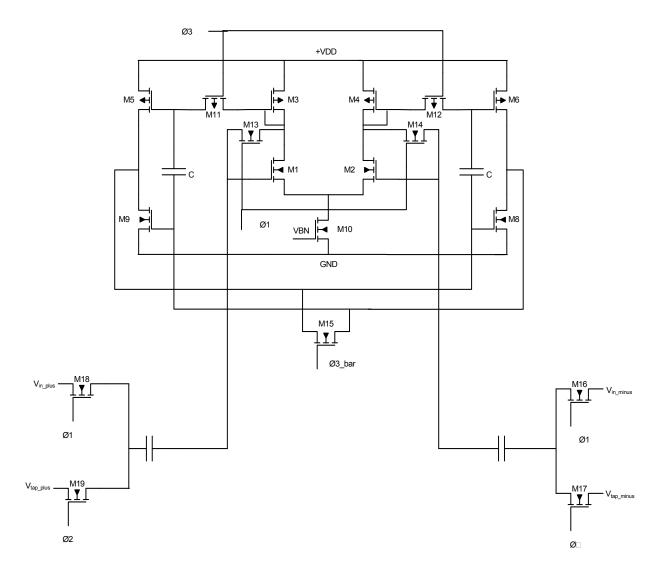

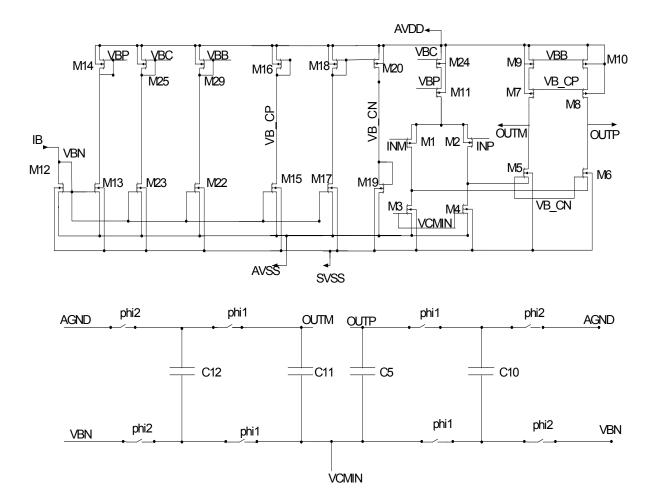

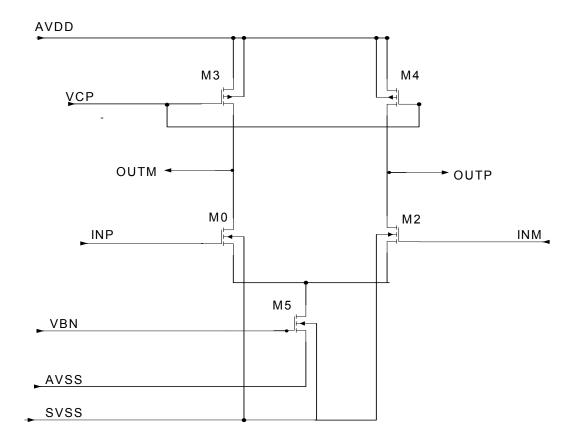

The OTA used in the residue generator is a folded cascade amplifier with switched-capacitor common-mode feedback. The capacitors in the common-mode feedback all have a value of 1 pF. The OTA schematic is illustrated in Figure 3.11. The bias current flowing in device  $M_{24}$  is 300  $\mu A$ .

Figure 3.10: Residue generator circuit

The OTA described above meets the following specifications:

- Input common mode range of 2.25 V to 2.75 V

- Operate from a supply voltage of 4.75 V to 5.25 V

- Slewing time of 10 ns and a linear settling time of 90 ns

- Drive load capacitances between 1 pF and 5 pF

- Phase Margin of 60 degrees across all corners

- Low frequency open loop gain of 70 dB across all corners

- Total input referred integrated noise less than 100 µV

- Input offset voltage less than 6 mV

- Common Mode Rejection Ration of 60 dB

- Output voltage swing of +/- 200 mV

Figure 3.11: OTA schematic

The OTA frequency response using the typical process corner is as shown in Figure 3.12. As seen in figure, the low-frequency open-loop gain is 71 dB. The OTA

has a GBW of 30 MHz with a phase margin of 60 degrees when driving a 5 pF load. Table 3.2 gives the Gain and phase margin for multiple process corners and loads.

| Load = 1 pF  | Typical  | Worst case speed | Worst case power |

|--------------|----------|------------------|------------------|

| Phase margin | 59.1     | 58               | 60               |

| Gain         | 71.9 dB  | 71.9 dB          | 72               |

| Bandwidth    | 75 MHz   | 81 MHz           | 81 MHz           |

| Load = 5 pF  |          |                  |                  |

| Phase Margin | 58.50    | 58.2             | 58.5             |

| Gain         | 71.9 dB  | 71.9 dB          | 71.8 dB          |

| Bandwidth    | 29.4 MHz | 28.2 MHz         | 31.7 MHz         |

Table 3.2: Gain and phase margin of OTA for multiple process corners

Figure 3.12: OTA frequency response

The OTA meets all the above specifications across all tested (typical, worst-case speed, and worst-case power). The input differential pair in the OTA possesses a large transconductance which is the key feature responsible the fast response time of the residue generator. The sizes of all the transistors used in the OTA schematic are as shown in Table 3.3.

| Transistor | Type | Width(µm) | Length(µm) | Multiplier |

|------------|------|-----------|------------|------------|

| M1         | p    | 50        | 0.6        | 4          |

| M2         | p    | 50        | 0.6        | 4          |

| М3         | n    | 4         | 10         | 9          |

| M4         | n    | 4         | 10         | 9          |

| M5         | n    | 40        | 2.2        | 4          |

| M6         | n    | 40        | 2.2        | 4          |

| M7         | p    | 63        | 1.1        | 4          |

| M8         | p    | 63        | 1.1        | 4          |

| M9         | p    | 33.6      | 9          | 2          |

| M10        | p    | 33.6      | 9          | 2          |

| M11        | p    | 66        | 0.6        | 4          |

| M12        | n    | 4         | 10         | 2          |

| M13        | n    | 4         | 10         | 6          |

| M14        | p    | 6         | 0.6        | 1          |

| M15        | n    | 4         | 10         | 6          |

| M16        | p    | 24.8      | 9.2        | 2          |

| M17        | n    | 4         | 10         | 2          |

| M18        | p    | 50.4      | 10         | 2          |

| M19        | n    | 14.5      | 7.5        | 1          |

| M20        | P    | 50.4      | 10         | 6          |

| M22        | n    | 4         | 10         | 6          |

| M23        | n    | 4         | 10         | 6          |

| M24        | p    | 24        | 1.5        | 3          |

| M25        | p    | 24        | 1.5        | 3          |

| M29        | p    | 33.6      | 9          | 2          |

Table 3.3: Transistor sizes for OTA schematic

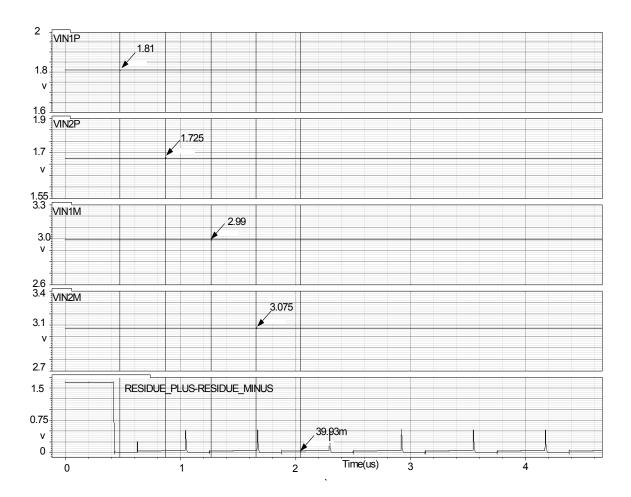

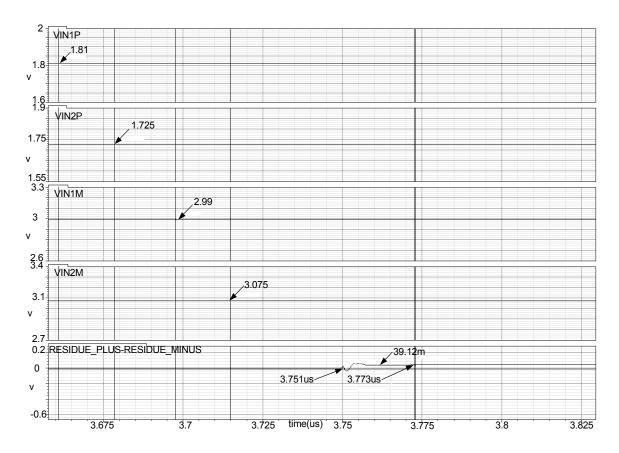

Figure 3.13 shows a pair of inputs to the residue generator and its output. Figure 3.14 shows the settling behavior of the residue generator. It can be seen that the residue generator settles to its final value within 20 nanoseconds.

The residue generator offset voltage does not affect the linearity of the ADC as long as it does not drive the input to the second stage out of range covered by the digital correction. The residue generator is implemented in a fully differential configuration and offset-cancellation is performed so the residual offset is primarily due to charge injection mismatch between the switches and capacitor mismatches.

Figure 3.13: Residue generator output

Figure 3.14: Settling behavior of residue generator

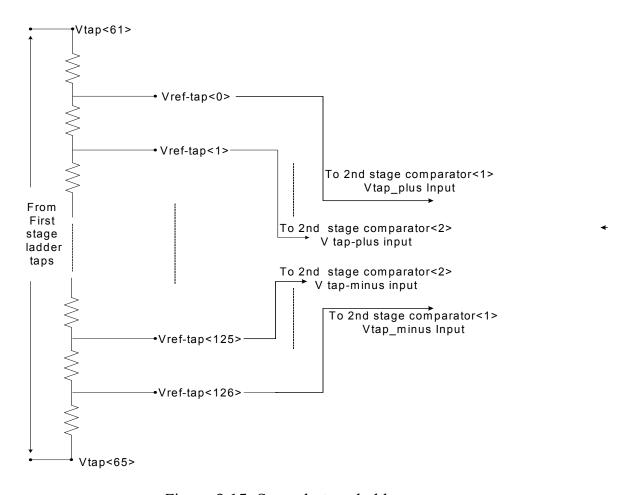

# Second Stage Ladder and Ladder Correction Circuit

The differential reference voltages in the second stage are generated using the second-stage ladder. The first-stage ladder divides the bandgap voltage (V<sub>ref\_plus</sub>-V<sub>Ref\_minus</sub>) into 64 equal segments. The second-stage ladder divides one of these segments into 64 sub segments each 1 LSB wide. The second stage ladder thus provides differential reference voltages from 1 to 64 LSB. The segment of the first-stage ladder that is divided into 64 sub-segments is at the midpoint of the first-stage ladder so that the common-mode voltage of the differential reference voltage is near AGND (2.4 Volts). As shown in Figure 3.15, each resistor in the second-stage ladder is constructed from "NY" poly.

Figure 3.15: Second-stage ladder

As in the first-stage ladder, a resistance of  $40\Omega$  is sufficient for matching purposes. Thus a length of  $10\,\mu$ m and a width of  $12.5\,\mu$ m is used for each NY resistor in the ladder. The taps from the first-stage ladder are labeled as Vtap's and second stage taps are labeled as Vref\_tap's. Figure 3.15 illustrates how the differential tap voltages are applied to the second-stage comparators.

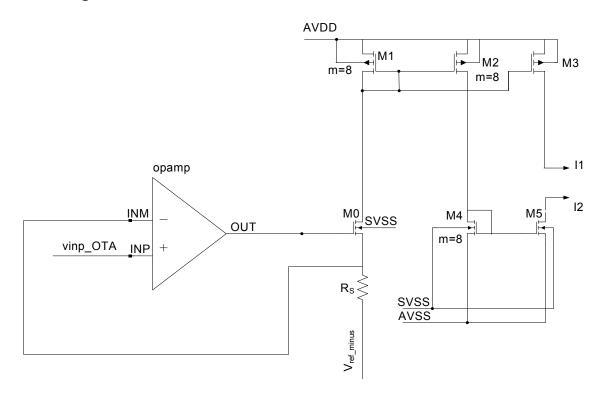

The loading on the first-stage ladder caused by the addition of the secondstage ladder, leads to a systematic error in the differential voltages generated by the first stage ladder. This results in comparators firing wrongly in the first stage. To avoid this, currents drawn by the second-stage ladder from the first-stage ladder are cancelled using a ladder loading correction circuit [Raz:92]. As shown in Figure 3.16, the correction circuit injects currents  $I_1$  and  $I_2$  at the junction nodes of the two ladders. The magnitude of the currents equal that of currents drawn by second-stage ladder.

Figure 3.16: Ladder correction circuit

We observe that

$I_1$  =  $I_2$  = (voltage across second stage ladder)/(total resistance of ladder) Therefore,

$$I_1 = I2 = (128LSB)/(128R_u) = 14.64 \mu A.$$

where R<sub>u</sub> is the unit resistor in the second stage ladder.

The ladder loading correction circuit consists of a voltage-to-current converter and current mirror circuits. The voltage-to-current converter is made up of the operational amplifier, resistor  $R_{\rm S}(=8R_{\rm u})$  and transistor  $M_0$ . It produces a current of (64LSB)/8 $R_{\rm u}$ . Transistors  $M_1$ - $M_5$  divide this current by a factor of 8 to generate  $I_1$  and  $I_2$ . Currents  $I_1$  and  $I_2$  track  $R_{\rm u}$  thus maintaining the loading

correction over variations in temperature and resistor values. An op amp [Pro:07] which was originally designed for the PSD8C chip was used in the circuit of Figure 3.16. Table 3.4 lists the sizes of all the transistors used in the ladder correction circuit.

| Transistor | Type | Width | Length | Multiplier |

|------------|------|-------|--------|------------|

| MO         | n    | 31.7  | 0.6    | 10         |

| M1         | р    | 12    | 10     | 8          |

| M2         | р    | 12    | 10     | 8          |

| М3         | р    | 12    | 10     | 1          |

| M4         | n    | 10    | 5      | 8          |

| M4         | n    | 10    | 5      | 1          |

Table 3.4: Transistor sizes for ladder correction circuit

# Second Stage Comparator